# **Diskette Drive Controller**

The diskette drive controller and connector reside on the system board. In the Model 50 system, an interposer board plugs into the controller connector and provides connection for the diskette drives. In the Model 60 system a cable is used to connect the diskette drives to the system board.

Note: This section is included as a guide to compatibility for existing software. New software should access the diskette drive controller through BIOS.

The diskette drive controller supports:

- Two drives

- 1M byte unformatted media, 720K formatted

- 2M byte unformatted media, 1.44M formatted

- 250,000 bits-per-second mode

- 500,000 bits-per-second mode.

Precompensation of 125 nanoseconds is provided for all cylinders.

The diskette drive controller reads and writes both high- and low-density media. The 720K and 1.44M formatted diskette densities are supported for single and multithread operations.

**Warning:** 16-bit operations to the video subsystem can cause a diskette overrun in the 1.44M mode because data width conversions may require more than 12 microseconds. If an overrun occurs, BIOS returns an error code and the operation should be retried.

When switching from one density to another, the following changes occur:

- The clock rate changes.

- Eight MHz for high density

- Four MHz for low density

- The step rate changes.

**Warning:** The diskette controller does not check if the media supports the density selected. 1M media may not be reliably formatted to the 2M density and loss of data may result.

# Registers

The diskette drive controller has five registers; three registers show the status of signals used in diskette operations, and two registers control certain interface signals. Two additional registers are accessed by the system microprocessor: the Diskette Drive Controller Status register and the Data register.

Status Register A: Status Register A, hex address 03F0, is a read-only register that shows the status of the corresponding signals.

| Bit | Function             |

|-----|----------------------|

| 7   | Interrupt Pending    |

| 6   | -2nd Drive Installed |

| 5   | Step                 |

| 4   | -Track 0             |

| 3   | Head 1 Select        |

| 2   | -Index               |

| 1 1 | -Write Protect       |

| 0   | Direction            |

Figure 4-120. Status Register A (Hex 03F0)

**Status Register B:** Status Register B, address hex 03F1, is a read-only register that shows the status of signals between the diskette drive and the controller.

| Bit  | Function                                                                 |

|------|--------------------------------------------------------------------------|

| 7, 6 | Reserved                                                                 |

| 5    | Drive Select                                                             |

| 4    | Write Data (A positive transition on WR DATA causes this bit to toggle.) |

| 3    | Read Data (A positive transition on -RD DATA causes this bit to toggle.) |

| 2    | Write Enable                                                             |

| 1    | Motor Enable 1                                                           |

| 0    | Motor Enable 0                                                           |

Figure 4-121. Status Register B (Hex 03F1)

**Digital Output Register:** The Digital Output register, address hex 03F2, is write-only and used to control drive motors, drive selection, and feature enable. All bits are cleared by a Reset.

| Bit         | Function                                        |  |

|-------------|-------------------------------------------------|--|

| 7, 6        | Reserved                                        |  |

| 5           | Motor Enable 1 *                                |  |

| 4           | Motor Enable 0 *                                |  |

| 3           | Reserved                                        |  |

| 2           | -8272A Reset                                    |  |

| 1           | Reserved                                        |  |

| Ö           | Drive Select (0 = Drive 0, 1 = Drive 1) *       |  |

| The Motor E | nable bit is qualified by the Drive Select bit. |  |

Figure 4-122. Digital Output Register (Hex 03F2)

**Digital Input Register:** The Digital Input register, address hex 03F7, is read-only and used to sense the state of the '-diskette change' signal and '-high density select' signal.

| Bit   | Function             |  |

|-------|----------------------|--|

| 7     | Diskette Change      |  |

| 6 - 1 | Reserved             |  |

| 0     | -High Density Select |  |

Figure 4-123. Digital Input Register (Hex 03F7)

Configuration Control Register: The Configuration Control register, address hex 03F7, is write-only and used to set the transfer rate.

| Bit   | Function              |

|-------|-----------------------|

| 7 - 2 | Reserved              |

| 1, 0  | DRC1, DRC0            |

| ., •  | 00 = 500,000-bit mode |

|       | 01 = Reserved         |

|       | 10 = 250,000-bit mode |

|       | 11 = Reserved         |

Figure 4-124. Configuration Register (Hex 03F7)

**Diskette Drive Controller Status Register:** This is a read-only register and is used to facilitate the transfer of data between the system microprocessor and the controller.

| Bit | Function                 |

|-----|--------------------------|

| 7   | Request for Master       |

| 6   | Data Input/Output        |

| 5   | Non-DMA Mode             |

| 4   | Diskette Controller Busy |

| 3   | Reserved                 |

| 2   | Reserved                 |

| 1   | Drive 1 Busy             |

| 0   | Drive 0 Busy             |

Figure 4-125. Diskette Drive Controller Status Register (Hex 03F4)

- Bit 7 When this bit is set to 1, the Data register is ready for transfer with the system microprocessor.

- Bit 6 This bit indicates the direction of data transfer between the diskette drive controller and the system microprocessor. If this bit is set to 1, the transfer is from the controller to the system microprocessor; if it is set to 0, the transfer is from the microprocessor.

- Bit 5 When this bit is set to 1, the controller is in the non-DMA mode.

- Bit 4 When this bit is set to 1, a Read or Write command is being executed.

- Bit 3, 2 Reserved

- Bit 1 Drive 1 Busy When set to 1, diskette drive 1 is in the seek mode.

- Bit 0 Drive 0 Busy When set to 1, diskette drive 0 is in the seek mode.

Data Registers, Hex 03F5: Address hex 03F5, consists of several registers in a stack with only one register presented to the data bus at a time. It stores data, commands, and parameters, and provides diskette-drive status information. Data bytes are passed through the Data register to program or obtain results after a command.

# **Diskette Drive Controller Programming Considerations**

Each command is initiated by a multibyte transfer from the system microprocessor, and the result can also be a multibyte transfer back to the system microprocessor. Because of this multibyte interchange of information between the controller and the microprocessor, each command is considered to consist of three phases:

Command Phase: The system microprocessor issues a series of Writes to the controller that direct it to perform a specific operation.

Execution Phase: The controller performs the specified operation.

Result Phase: After completion of the operation, status and other housekeeping information is made available to the system microprocessor through a sequence of Read commands to the system microprocessor.

The following is a summary of the commands that are issued to the diskette drive controller.

- Read Data command

- Read Deleted Data command

- Read a Track command

- Read ID command

- Write Data command

- Write Deleted Data command

- Format a Track command

- Scan Equal command

- Scan Low or Equal command

- Scan High or Equal command

- Recalibrate command

- Sense Interrupt Status command

- Specify command

- Sense Drive Status command

- Seek command.

The following figure shows the symbols used in the format of the individual commands. The individual command formats start on page 4-133.

| Symbol | Name                | Description                                                                                                          |

|--------|---------------------|----------------------------------------------------------------------------------------------------------------------|

| С      | Cylinder Number     | C contains the current or<br>selected cylinder number<br>in binary notation.                                         |

| D      | Data                | D contains the data pattern to be written to a sector.                                                               |

| D7-D0  | Data Bus            | An 8-bit data bus in which D7 is the most-significant bit and D0 is the least significant.                           |

| DTL    | Data Length         | When N is 00, DTL is the data<br>length to be read from or<br>written to a sector.                                   |

| EOT    | End of Track        | The final sector number on a cylinder.                                                                               |

| GPL    | Gap Length          | The length of gap 3 (spacing between sectors excluding the voltage controlled oscillator synchronous field).         |

| н      | Head Address        | The head number, either 0 or 1, as specified in the ID field.                                                        |

| HD     | Head                | The selected head number, 0 or 1. (H=HD in all command words.)                                                       |

| HLT    | Head Load Time      | The head load time in the selected drive (2 to 254 milliseconds in 2-millisecond increments).                        |

| HUT    | Head Unload<br>Time | The head unload time after a<br>Read or Write operation (16<br>to 240 milliseconds in<br>16-millisecond increments). |

| MF     | FM or MFM<br>Mode   | A 0 selects FM mode and a 1 selects MFM.                                                                             |

| мт     | Multitrack          | A 1 selects multitrack operation.<br>(Both HD0 and HD1 will be read<br>or written.)                                  |

| L      |                     |                                                                                                                      |

Figure 4-126 (Part 1 of 2). Command Symbols, Diskette Drive Controller

| Symbol      | Name                       | Description                                                                                                                                                                                 |

|-------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N           | Number                     | The number of data bytes written in a sector.                                                                                                                                               |

| NCN         | New Cylinder<br>Number     | The new cylinder number for a seek operation.                                                                                                                                               |

| ND          | Non-DMA Mode               | This indicates an operation in the non-DMA mode.                                                                                                                                            |

| PCN         | Present Cylinder<br>Number | The cylinder number at the completion of a Sense Interrupt Status command (present position of the head).                                                                                   |

| R           | Record                     | The sector number to be read or written.                                                                                                                                                    |

| sc          | Sector                     | The number of sectors per cylinder.                                                                                                                                                         |

| sĸ          | Skip                       | This stands for skip<br>deleted-data address mark.                                                                                                                                          |

| SRT         | Step Rate                  | The stepping rate for the diskette drive (1 to 16 milliseconds in 1-millisecond increments).                                                                                                |

| ST 0 - ST 3 | Status 0-Status 3          | Four registers that store status information after a command is executed.                                                                                                                   |

| STP         | Scan Test                  | If STP is 1, the data in contiguous sectors is compared with the data sent by the system microprocessor during a scan operation. If STP is 2, then afternate sectors are read and compared. |

| US0 - US1   | Unit Select                | The selected drive number encoded the same as bits 0 and 1 of the Digital Output register.                                                                                                  |

Figure 4-126 (Part 2 of 2). Command Symbols, Diskette Drive Controller

The following are commands that are issued to the controller. An X is used to indicate a don't care condition.

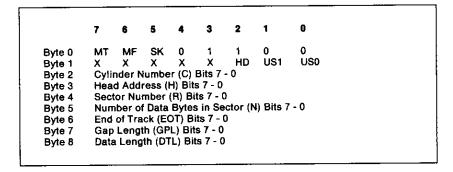

#### **Read Data Command Format**

#### Command Phase

MT = Multitrack

MF = MFM mode

SK = Skip deleted-data address mark

HD = Head number

USx = Unit select

```

2

Byte 0

SK

MF

Х

HD

US1

US<sub>0</sub>

Byte 1

Х

Х

Х

Х

Byte 2

Cylinder Number (C) Bits 7 - 0

Byte 3

Head Address (H) Bits 7 - 0

Byte 4

Sector Number (R) Bits 7 - 0

Number of Data Bytes in Sector (N) Bits 7 - 0

Byte 5

Byte 6

End of Track (EOT) Bits 7 - 0

Byte 7

Gap Length (GPL) Bits 7 - 0

Data Length (DTL) Bits 7 - 0

Byte 8

```

Figure 4-127. Read Data Command

```

Byte 0

Status Register 0 (ST 0) Bits 7 - 0

Byte 1

Status Register 1 (ST 1) Bits 7 - 0

Status Register 2 (ST 2) Bits 7 - 0

Byte 2

Cylinder Number (C) Bits 7 - 0

Byte 3

Byte 4

Head Address (H) Bits 7 - 0

Sector Number (R) Bits 7 - 0

Byte 5

Byte 6

Number of Data Bytes in Sector (N) Bits 7 - 0

```

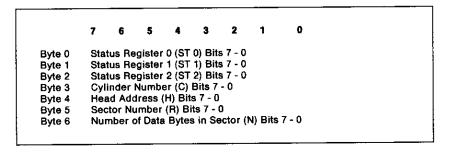

Figure 4-128. Read Data Result

#### **Read Deleted Data Command Format**

#### Command Phase

MT = Multitrack

MF = MFM mode

SK = Skip deleted-data address mark

HD = Head number

USx = Unit select

Figure 4-129. Read Deleted Data Command

Figure 4-130. Read Deleted Data Result

#### **Read a Track Command Format**

#### Command Phase

MF = MFM mode

SK = Skip deleted-data address mark

HD = Head number

USx = Unit select

```

5

Byte 0

MF

SK

0

Byte 1

US1

US0

Х

Х

Х

Х

Х

HD

Byte 2

Cylinder Number (C) Bits 7 - 0

Byte 3

Head Address (H) Bits 7 - 0

Byte 4

Sector Number (R) Bits 7 - 0

Byte 5

Number of Data Bytes in Sector (N) Bits 7 - 0

Byte 6

End of Track (EOT) Bits 7 - 0

Gap Length (GPL) Bits 7 - 0

Byte 7

Byte 8

Data Length (DTL) Bits 7 - 0

```

Figure 4-131. Read a Track Command

```

Byte 0

Status Register 0 (ST 0) Bits 7 - 0

Byte 1

Status Register 1 (ST 1) Bits 7 - 0

Status Register 2 (ST 2) Bits 7 - 0

Byte 2

Cylinder Number (C) Bits 7 - 0

Byte 3

Byte 4

Head Address (H) Bits 7 - 0

Byte 5

Sector Number (R) Bits 7 - 0

Byte 6

Number of Data Bytes in Sector (N) Bits 7 - 0

```

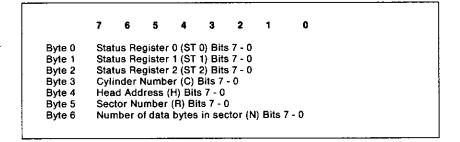

Figure 4-132. Read a Track Result

#### **Read ID Command Format**

#### Command Phase

MF = MFM mode HD = Head number USx = Unit select

```

1

0

7

3

2

0

Byte 0

0

MF

1

Х

US1

US0

Х

Х

Х

HD

Byte 1

```

Figure 4-133. Read ID Command

#### Result Phase

6 5 4 3 2 1 0 Status Register 0 (ST 0) Bits 7 - 0 Byte 0 Status Register 1 (ST 1) Bits 7 - 0 Byte 1 Byte 2 Status Register 2 (ST 2) Bits 7 - 0 Cylinder Number (C) Bits 7 - 0 Byte 3 Head Address (H) Bits 7 - 0 Byte 4 Sector Number (R) Bits 7 - 0 Byte 5 Number of Data Bytes in Sector (N) Bits 7 - 0 Byte 6

Figure 4-134. Read ID Result

#### **Write Data Command Format**

#### Command Phase

```

MT = Multitrack

MF = MFM mode

HD = Head number

USx = Unit select

```

```

5

3

2

0

0

0

1

Byte 0

MT

US1

US0

Byte 1

Х

Х

Х

Х

Х

HD

Cylinder Number (C) Bits 7 - 0

Byte 2

Byte 3

Head Address (H) Bits 7 - 0

Byte 4

Sector Number (R) Bits 7 - 0

Byte 5

Number of Data Bytes in Sector (N) Bits 7 - 0

End of Track (EOT) Bits 7 - 0

Byte 6

Gap Length (GPL) Bits 7 - 0

Byte 7

Data Length (DTL) Bits 7 - 0

Byte 8

```

Figure 4-135. Write Data Command

```

3

2

7

Byte 0

Status Register 0 (ST 0) Bits 7 - 0

Byte 1

Status Register 1 (ST 1) Bits 7 - 0

Status Register 2 (ST 2) Bits 7 - 0

Byte 2

Cylinder Number (C) Bits 7 - 0

Byte 3

Byte 4

Head Address (H) Bits 7 - 0

Sector Number (R) Bits 7 - 0

Byte 5

Byte 6

Number of Data Bytes in Sector (N) Bits 7 - 0

```

Figure 4-136. Write Data Result

## Write Deleted Data Command Format

#### Command Phase

MT = Multitrack

MF = MFM mode

HD = Head number

USx = Unit select

```

0

2

1

5

3

MT

MF

0

0

Byte 0

HD

US1

US0

Х

Х

Х

Byte 1

Х

Х

Cylinder Number (C) Bits 7 - 0

Byte 2

Head Address (H) Bits 7 - 0

Byte 3

Sector Number (R) Bits 7 - 0

Byte 4

Byte 5

Number of Data Bytes in Sector (N) Bits 7 - 0

End of Track (EOT) Bits 7 - 0

Byte 6

Gap Length (GPL) Bits 7 - 0

Byte 7

Data Length (DTL) Bits 7 - 0

Byte 8

```

Figure 4-137. Write Deleted Data Command

```

1

0

Status Register 0 (ST 0) Bits 7 - 0

Byte 0

Status Register 1 (ST 1) Bits 7 - 0

Byte 1

Byte 2

Status Register 2 (ST 2) Bits 7 - 0

Cylinder Number (C) Bits 7 - 0

Byte 3

Byte 4

Head Address (H) Bits 7 - 0

Sector Number (R) Bits 7 - 0

Byte 5

Number of Data Bytes in Sector (N) Bits 7 - 0

Byte 6

```

Figure 4-138. Write Deleted Data Result

## **Format a Track Command Format**

#### Command Phase

```

MF = MFM mode

HD = Head number

USx = Unit select

```

```

2

1

0

MF

0

1

Byte 0

Byte 1

Х

Х

Х

Х

Х

HD

US1

US0

Number of Data Bytes in Sector (N) Bits 7 - 0

Byte 2

Sectors per Cylinder (SC) Bits 7 - 0

Byte 3

Gap Length (GPL) Bits 7 - 0

Byte 4

Byte 5

Data (D) Bits 7 - 0

```

Figure 4-139. Format a Track Command

Figure 4-140. Format a Track Result

# Scan Equal Command Format

#### Command Phase

MT = Multitrack

MF = MFM mode

SK = Skip deleted-data address mark

HD = Head number

USx = Unit select

```

1

0

5 4

3

2

7

6

Byte 0

SK

0

0

MT

MF

US1

US0

Byte 1

Х

Х

HD

Х

Х

Х

Cylinder Number (C) Bits 7 - 0

Byte 2

Head Address (H) Bits 7 - 0

Byte 3

Sector Number (R) Bits 7 - 0

Byte 4

Byte 5

Number of Data Bytes in Sector (N) Bits 7 - 0

Byte 6

Byte 7

Byte 6

End of Track (EOT) Bits 7 - 0

Gap Length (GPL) Bits 7 - 0

Scan Test (STP) Bits 7 - 0

Byte 8

```

Figure 4-141. Scan Equal Command

```

2

1

0

5 4

Status Register 0 (ST 0) Bits 7 - 0

Byte 0

Status Register 1 (ST 1) Bits 7 - 0

Byte 1

Status Register 2 (ST 2) Bits 7 - 0

Byte 2

Byte 3

Cylinder Number (C) Bits 7 - 0

Head Address (H) Bits 7 - 0

Byte 4

Sector Number (R) Bits 7 - 0

Byte 5

Number of Data Bytes in Sector (N) Bits 7 - 0

Byte 6

```

Figure 4-142. Scan Equal Result

# Scan Low or Equal Command Format

#### Command Phase

MT = Multitrack

MF = MFM mode

SK = Skip deleted-data address mark

HD = Head number

USx = Unit select

```

7

6

5

3

2

1

0

MF

Byte 0

MT

SK

1

1

0

US1

US0

Byte 1

Х

Х

х

Х

HD

Byte 2

Cylinder Number (C) Bits 7 - 0

Byte 3

Head Address (H) Bits 7 - 0

Byte 4

Sector Number (R) Bits 7 - 0

Number of Data Bytes in Sector (N) Bits 7 - 0

Byte 5

End of Track (EOT) Bits 7 - 0

Byte 6

Byte 7

Gap Length (GPL) Bits 7 - 0

Byte 8

Scan Test (STP) Bits 7 - 0

```

Figure 4-143. Scan Low or Equal Command

```

2

6

5

1

0

Byte 0

Status Register 0 (ST 0) Bits 7 - 0

Byte 1

Status Register 1 (ST 1) Bits 7 - 0

Byte 2

Status Register 2 (ST 2) Bits 7 - 0

Byte 3

Cylinder Number (C) Bits 7 - 0

Byte 4

Head Address (H) Bits 7 - 0

Sector Number (R) Bits 7 - 0

Byte 5

Number of Data Bytes in Sector (N) Bits 7 - 0

Byte 6

```

Figure 4-144. Scan Low or Equal Result

# Scan High or Equal Command Format

#### Command Phase

MT = Multitrack

MF = MFM mode

SK = Skip deleted-data address mark

HD = Head number

USx = Unit select

```

7

6

5

3

2

1

0

Byte 0

MT

MF

SK

HD

US1

US<sub>0</sub>

Byte 1

Х

х

Х

Х

Х

Byte 2

Cylinder Number (C) Bits 7 - 0

Byte 3

Head Address (H) Bits 7 - 0

Byte 4

Sector Number (R) Bits 7 - 0

Number of Data Bytes in Sector (N) Bits 7 - 0

Byte 5

Byte 6

End of Track (EOT) Bits 7 - 0

Byte 7

Gap Length (GPL) Bits 7 - 0

Byte 8

Scan Test (STP) Bits 7 - 0

```

Figure 4-145. Scan High or Equal Command

```

2

1

0

Byte 0

Status Register 0 (ST 0) Bits 7 - 0

Status Register 1 (ST 1) Bits 7 - 0

Byte 1

Byte 2

Status Register 2 (ST 2) Bits 7 - 0

Cylinder Number (C) Bits 7 - 0

Byte 3

Byte 4

Head Address (H) Bits 7 - 0

Byte 5

Sector Number (R) Bits 7 - 0

Byte 6

Number of Data Bytes in Sector (N) Bits 7 - 0

```

Figure 4-146. Scan High or Equal Result

#### **Recalibrate Command Format**

#### Command Phase

USx = Unit select

|        | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

|--------|---|---|---|---|---|---|-----|-----|

| Byte 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1   | 1   |

| Byte 1 | X | Х | Х | Х | Х | 0 | US1 | US0 |

Figure 4-147. Recalibrate Command

Result Phase: This command has no result phase.

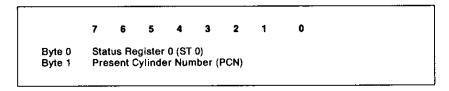

## **Sense Interrupt Status Command Format**

#### Command Phase

Figure 4-148. Sense Interrupt Status Command

Figure 4-149. Sense Interrupt Status Result

# **Specify Command Format**

#### Command Phase

SRT = Diskette stepping rate

HUT = Head unload time

HLT = Head load time

ND = Non-data mode

|                            | 7               | 6   | 5   | 4   | 3   | 2   | 1   | 0 |

|----------------------------|-----------------|-----|-----|-----|-----|-----|-----|---|

| Byte 0<br>Byte 1<br>Byte 2 | 0<br>SRT<br>HLT | SRT | SRT | SRT | HUT | HUT | HUT |   |

Figure 4-150. Specify Command

Result Phase: This command has no result phase.

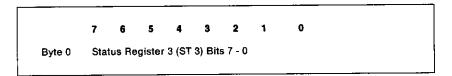

#### **Sense Drive Status Command Format**

#### Command Phase

HD = Head number USx = Unit select

| · · · · · ·      | 7 | 6 | 5 | 4 | 3 | 2       | 1        | 0        |

|------------------|---|---|---|---|---|---------|----------|----------|

| Byte 0<br>Byte 1 |   |   |   |   |   | †<br>HD | 0<br>US1 | 0<br>US0 |

Figure 4-151. Sense Drive Status Command

#### Result Phase

Figure 4-152. Sense Drive Status Result

# 4-144 I/O Controllers, Diskette Drive

#### **Seek Command Format**

#### Command Phase

USx = Unit select HD = Head select

|        | 7   | 6       | 5      | 4     | 3       | 2      | 1        | 0       |

|--------|-----|---------|--------|-------|---------|--------|----------|---------|

| Byte 0 | 0   | 0       | 0      | 0     | 1       | 1      | 1        | 1       |

| Byte 1 |     |         |        |       |         |        |          | US0     |

| Byte 2 | Nev | v Cylin | nder N | lumbe | r for S | eek (N | CN) Bits | s 7 - 0 |

Figure 4-153. Seek Command

Result Phase: This command has no result phase.

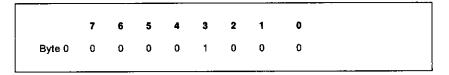

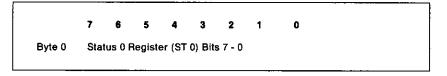

#### **Invalid Command Format**

Result Phase: The following status byte is returned to the system microprocessor when an invalid command has been received.

Figure 4-154. Invalid Command Result

# **Command Status Registers**

The following are definitions of status registers ST 0 through ST 3.

Status Register 0: The following are bit definitions of status register ST 0.

| Bit  | Function                                                                                                                                                                                                                        |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 6 | Interrupt Code (IC)                                                                                                                                                                                                             |

|      | 00 = Normal Termination of Command (NT) - The<br>command was completed and properly executed.                                                                                                                                   |

| Į.   | 01 = Abrupt Termination of Command (AT) -<br>The execution of the command was started but not<br>successfully completed.                                                                                                        |

| i.   | 10 = Invalid Command Issue (IC) - The issued command was never started.                                                                                                                                                         |

|      | 11 = Reserved                                                                                                                                                                                                                   |

| 5    | Seek End (SE) - Set to 1 when the diskette drive completes the Seek command.                                                                                                                                                    |

| 4    | Equipment Check (EC) - Set to 1 if the '-track 0' signal fails to occur after 77 step pulses (Recalibrate command).                                                                                                             |

| 3    | Not Ready (NR) - This flag is set to 1 when the diskette drive is in the not-ready state and a Read or Write command is issued. It is also set if a Read or Write command is issued to side 1 of a single-sided diskette drive. |

| 2    | Head Address (HD) - indicates the state of the head at interrupt.                                                                                                                                                               |

| 1    | Unit select 1 (US 1) - Indicates drive 1 is at interrupt.                                                                                                                                                                       |

| 0    | Unit select 0 (US 0) - Indicates drive 0 is at interrupt.                                                                                                                                                                       |

Figure 4-155. Status Register 0 (ST 0)

# Status Register 1: The following are bit definitions of status register ST 1.

| Bit | Function                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | End of Cylinder (EN) - Set to 1 when the controller tries to gain access to a sector beyond the final sector of a cylinder.                                                                                                                                                                                                                                                                         |

| 6   | Reserved - This bit is always set to 0.                                                                                                                                                                                                                                                                                                                                                             |

| 5   | Data Error (DE) - Set to 1 when the controller detects a CRC error in either the ID field or the data field.                                                                                                                                                                                                                                                                                        |

| 4   | Overrun (OR) - Set to 1 if the controller is not serviced by the main system within a certain time limit during data transfers.                                                                                                                                                                                                                                                                     |

| 3   | Reserved - This bit is always set to 0.                                                                                                                                                                                                                                                                                                                                                             |

| 2   | No Data (ND) - Set to 1 if the controller cannot find the sector specified in the ID register during the execution of a Read Data, Write Deleted Data, or Scan command. This flag is also set to 1 if the controller cannot read the ID field without an error during the execution of a Read ID command or if the starting sector cannot be found during the execution of a Read Cylinder command. |

| 1   | Not Writable (NW) - Set to 1 if the controller detects a '-write-protect' signal from the diskette drive during execution of a Write Data, Write Deleted Data, or Format Cylinder command.                                                                                                                                                                                                          |

| 0   | Missing Address Mark (MA) - Set to 1 if the controller cannot detect the ID address mark. At the same time, the MD of Status register 2 is set to 1.                                                                                                                                                                                                                                                |

Figure 4-156. Status Register 1 (ST 1)

# Status Register 2: The following are bit definitions of status register ST 2.

| Bit | Function                                                                                                                                                                       |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved - This bit is always set to 0.                                                                                                                                        |

| 6   | Control Mark (CM) - This flag is set to 1 if the controller encounters a sector that has a deleted data-address mark during execution of a Read Data or Scan command.          |

| 5   | Data Error in Data Field (DD) - Set to 1 if the controller detects an error in the data.                                                                                       |

| 4   | Wrong Cylinder (WC) - This flag is related to ND (no data) bit. When the contents of C on the medium are different from that stored in the ID register, this flag is set.      |

| 3   | Scan Equal Hit (SH) - Set to 1 if the contiguous sector data equals the processor data during the execution of a Scan command.                                                 |

| 2   | Scan Not Satisfied (SN) - Set to 1 if the controller cannot find a sector on the cylinder that meets the condition during a Scan command.                                      |

| 1   | Bad Cylinder (BC) - Related to ND; when the contents of C on the medium are different from that stored in the ID register, and the contents of C is FF, this flag is set to 1. |

| 0   | Missing Address Mark in Data Field (MD) - Set to 1 if the controller cannot find a data address mark or a deleted data address mark when data is read from the medium.         |

Figure 4-157. Status Register 2 (ST 2)

# Status Register 3: The following are bit definitions of status register ST 3.

| Bit  | Function                                                                            |  |

|------|-------------------------------------------------------------------------------------|--|

| 7    | Reserved                                                                            |  |

| 6    | Write Protect (WP) - Status of the '-write-protect' signal from the diskette drive. |  |

| 5    | Reserved                                                                            |  |

| 4    | Track 0 (T0) - Status of the '-track 0' signal from the diskette drive.             |  |

| 3    | Reserved                                                                            |  |

| 2    | Head Address (HD) - Status of the '-head 1 select' signal to the diskette drive.    |  |

| 1, 0 | Reserved                                                                            |  |

Figure 4-158. Status Register 3 (ST 3)

# **Signal Descriptions**

The diskette drive controller interface signal sequences and timings are all compatible with the industry standard 5.25 inch diskette interface. All interface signals are TTL compatible at the driver/receivers both in the rise and fall times as well as the interface levels.

The following describes the interface to the diskette drive.

# **Output Signals**

All output signals to the diskette drive operate between 5 Vdc and ground with the following definitions:

- The inactive level is 2.0 Vdc minimum.

- The active level is 0.8 Vdc maximum.

All inputs from the drive can sink 4.0 mA at the active (low) level.

- The inactive level is 3.7 Vdc minimum.

- The active level is 0.4 Vdc maximum.

The following are descriptions of the diskette drive controller output signals.

- -HIGH DENSITY SELECT: When active, the 2M mode is selected. Diskettes will be formatted with 18 sectors per track and a capacity of 1.44M. When inactive, the 1M mode is selected. Diskettes will be formatted with 9 sectors per track and a capacity of 720K. This signal is not used by the 720K diskette drive.

- -DRIVE SELECT 0 1: The drive select signals enable or disable all drive interface signals except -MOTOR ENABLE. When a drive select signal is active, the drive is enabled. When it is inactive, all controlled inputs are ignored, and all drive outputs are disabled.

- -MOTOR ENABLE 0 1: When this signal is made active, along with the proper drive select signals, the spindle starts to turn. There must be a 500-millisecond delay after -MOTOR ENABLE 0 or -MOTOR ENABLE 1 becomes active before a read, write, or seek operation. When inactive, this signal causes the spindle motor to decelerate and stop.

**-DIRECTION:** When this signal is active, -STEP moves the heads toward the drive spindle. When this signal is inactive, -STEP moves the heads away from the drive spindle. This signal is stable for 1 microsecond before and 1 microsecond after the trailing edge of the step pulse.

**Note:** After a direction change, a 15-millisecond delay is required before the next '-step' pulse.

**-STEP:** A 1-microsecond active pulse of this signal causes the read/write heads to move one track. The state of -DIRECTION at the trailing edge of -STEP determines the direction of motion.

Note: Before a read or write operation, a 15-millisecond seek settle time must be allowed.

**-WRITE DATA:** A 250-nanosecond pulse of this signal causes a bit to be written if -WRITE ENABLE is active. Data written on the diskette will have 125-nanosecond write-precompensation.

**-WRITE ENABLE:** When active, this signal enables the write current circuits, and -WRITE DATA controls the writing of information. Motor-start and head-settle times must be observed before this line becomes active.

-HEAD 1 SELECT: Making this signal active selects the upper head; otherwise the lower head is selected.

#### Input Signals

All inputs from the drive can sink 4.0 mA at the active (low) level.

- The inactive level is 3.7 Vdc minimum.

- The active level is 0.4 Vdc maximum.

-INDEX: When the drive senses the index, it generates an active pulse of at least 1 millisecond on this line. This signal is gated to the interface only when a diskette is in the drive.

-TRACK 0: This signal is active when the read/write head is on track 0. Track 0 is determined by a sensor, not a track counter.

The drive is able to seek to track 0 under control of the system even if there is no diskette inserted at the time. This is required so the system software can determine how many drives are attached to the system. Software selects each drive and attempts to recalibrate that drive to track 0. The track 0 indication is used to determine whether or not each drive is installed in the system.

- **-WRITE PROTECT:** When active, this signal indicates that a diskette with an open write-protect window (write-protected diskette) is in the drive, and the drive will not write.

- -READ DATA: Each bit detected provides a 250-nanosecond active pulse on this line for the 250,000 bit rate or a 125-nanosecond pulse for the 500,000 bit rate.

- -DISKETTE CHANGE: This signal is active at power-on and latched inactive when a diskette is present, the drive is selected, and a step pulse occurs. This signal goes active when the diskette is removed from the drive. The presence of a diskette is determined by a media sensor.

#### **Power Sequencing**

The WRITE GATE signal is turned off and is kept off before power is switched on or off. The read/write heads return to track 0 when the system power is switched on.

## Connector

The diskette drives for the Model 50 attach to the system board through an interposer board. The Model 60 diskette drives attach to the system board through a cable.

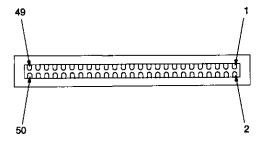

The diskette drive connector on the Model 50 system board is a 50-pin printed circuit board edge connector.

Figure 4-159. Model 50 Diskette Drive Controller Connector

The following are the voltages and signals assigned to the diskette drive controller connector.

| Pin No. | I/O | Signal Name   | Pin No. | 1/0 | Signal Name          |

|---------|-----|---------------|---------|-----|----------------------|

| 1       | I   | 2nd Drive     | 2       |     | -High Density Select |

| 3       | NA  | Ground        | 4       | NA  | Ground               |

| 5       | NA  | Ground        | 6       | NA  | Reserved             |

| 7       | NA  | Signal Ground | 8       | 1   | -Index               |

| 9       | NA  | Signal Ground | 10      | Ö   | -Motor Enable 0      |

| 11      | NA  | Signal Ground | 12      | ŏ   | -Drive Select 1      |

| 13      | NA  | Ground        | 14      | ŏ   | -Drive Select 0      |

| 15      | NA  | Signal Ground | 16      | ŏ   | -Motor Enable 1      |

| 17      | NA  | Signal Ground | 18      | ō   | -Direction           |

| 19      | NA  | Signal Ground | 20      | ŏ   | -Step                |

| 21      | NA  | Signal Ground | 22      | ō   | -Write Data          |

| 23      | NA  | Signal Ground | 24      | Õ   | -Write Enable        |

| 25      | NA  | Signal Ground | 26      | Ĭ   | -Track 0             |

| 27      | NA  | Signal Ground | 28      | i   | -Write Protect       |

| 29      | NA  | Signal Ground | 30      | i   | -Read Data           |

| 31      | NA  | Signal Ground | 32      | O   | -Head 1 Select       |

| 33      | NA  | Signal Ground | 34      | Ť   | -Diskette Change     |

| 35      | NA  | Ground        | 36      | NA  | Ground               |

| 37      | NA  | Ground        | 38      | NA  | +5 Vdc               |

| 39      | NA  | Ground        | 40      | NA  | + 12 Vdc             |

| 41      | NA  | Reserved      | 42      | NA  | Reserved             |

| 43      | NA  | Reserved      | 44      | NA  | Reserved             |

| 45      | NA  | Reserved      | 46      | NA  | Reserved             |

| 47      | NA  | Reserved      | 48      | NA  | Reserved             |

| 49      | NA  | Reserved      | 50      | NA  | Reserved             |

Figure 4-160. Model 50 Diskette Drive and Interposer Board Connector Voltage and Signal Assignments

The Model 60 system board has a single 2-by-20 pin connector for the attachment of one or two diskette drives. Signals and data are transmitted to and from the drives through a 40-wire L-shaped cable.

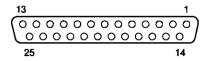

Figure 4-161. Model 60 Diskette Drive Controller Connector

The following are the voltages and signals assigned to the diskette drive controller connector.

| Pin No. | 1/0 | Signal Name            | Pin No. | 1/0 | Signal Name          |

|---------|-----|------------------------|---------|-----|----------------------|

| 1       | 1   | 2nd Drive<br>Installed | 2       | 0   | -High Density Select |

| 3       | NA  | Ground                 | 4       | NA  | Ground               |

| 5       | NA  | Ground                 | 6       | NA  | Reserved             |

| 7       | NA  | Signal Ground          | 8       | I   | -Index               |

| 9       | NA  | Signal Ground          | 10      | 0   | -Motor Enable 0      |

| 11      | NA  | Signal Ground          | 12      | 0   | -Drive Select 1      |

| 13      | NA  | Ground                 | 14      | 0   | -Drive Select 0      |

| 15      | NA  | Signal Ground          | 16      | 0   | -Motor Enable 1      |

| 17      | NA  | Signal Ground          | 18      | 0   | -Direction           |

| 19      | NA  | Signal Ground          | 20      | 0   | -Step                |

| 21      | NA  | Signal Ground          | 22      | 0   | -Write Data          |

| 23      | NA  | Signal Ground          | 24      | 0   | -Write Enable        |

| 25      | NA  | Signal Ground          | 26      | - 1 | -Track 0             |

| 27      | NA  | Signal Ground          | 28      | 1   | -Write Protect       |

| 29      | NA  | Signal Ground          | 30      | 4   | -Read Data           |

| 31      | NA  | Signal Ground          | 32      | 0   | -Head 1 Select       |

| 33      | NA  | Signal Ground          | 34      | - 1 | -Diskette Change     |

| 35      | NA  | Ground                 | 36      | NA  | Ground               |

| 37      | NA  | Ground                 | 38      | NA  | +5 Vdc               |

| 39      | NA  | Ground                 | 40      | NA  | + 12 Vdc             |

Figure 4-162. Model 60 Diskette Drive Controller Connector Voltage and Signal Assignments

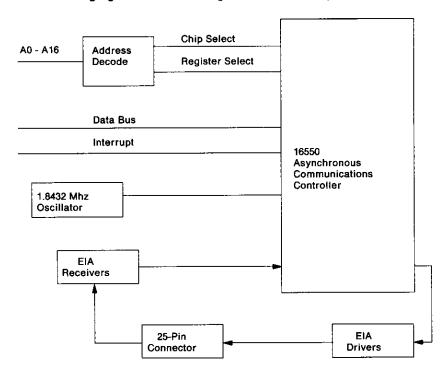

# Serial Port Controller

The serial port is controlled by a NS16550 serial communications controller. It is programmable and supports asynchronous communications. The controller automatically adds and removes start, stop, and parity bits. A programmable baud-rate generator allows operation from 50 baud to 19,200 baud. The port supports 5-, 6-, 7- and 8-bit characters with 1, 1.5, or 2 stop bits. A prioritized interrupt system controls transmit, receive, error, and line status as well as data-set interrupts.

The NS16550 controller is functionally compatible to the NS16450 controller. To programs, the NS16550 appears to be identical to the serial portion of the IBM Personal Computer AT Serial/Parallel adapter. Support for the controller is restricted to the functions which are identical to the NS16450. Using the controller in the FIFO mode may result in non-detectable data errors.

The serial port controller provides the following functions:

- Full double buffering in the character mode, eliminating the need for precise synchronization

- False-start bit detection

- Line-break generation and detection

- Modem control functions:

Clear to send (CTS)

Request to send (RTS)

Data set ready (DSR)

Data terminal ready (DTR)

Ring indicator (RI)

Data carrier detect (DCD).

The following figure is a block diagram of the serial port controller.

Figure 4-163. Serial Port Block Diagram

# **Communications Application**

The serial output port can be addressed as either serial output port 1 (Serial 1) or serial output port 2 (Serial 2). In this section port addresses contain an **n**. The **n** can be either a 3 for Serial 1 or a 2 for Serial 2. The selection of either port is discussed in "System Board Setup" on page 2-24.

Two interrupt lines are provided to the system. Interrupt level 4 (IRQ4) is for Serial 1 and interrupt level 3 (IRQ3) is for Serial 2. To allow the controller to send interrupts to the interrupt controller, bit 3 of the Modem Control register must be set to 1. At this point, any interrupts allowed by the Interrupt Enable register will cause an interrupt.

The data format is as follows:

| Mark- |     |    |    |    | _  |    |    |    | ·  | Parity | Stop |

|-------|-----|----|----|----|----|----|----|----|----|--------|------|

| ing   | Bit | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | Bit    | Bit  |

Figure 4-164. Serial Port, Data Format

Data bit 0 is the first bit to be sent or received. The controller automatically inserts the start bit, the correct parity bit (if programmed to do so), and the stop bits (1, 1.5, or 2, depending on the command in the Line Control register).

# **Programmable Baud-Rate Generator**

The controller has a programmable baud-rate generator that can divide the clock input (1.8432 MHz) by any divisor from 1 to 65,535. The output frequency of the baud-rate generator is the baud rate multiplied by 16. Two 8-bit latches store the divisor in a 16-bit binary format. These divisor latches must be loaded during setup to ensure desired operation of the baud-rate generator. When either of the divisor latches is loaded, a 16-bit baud counter is immediately loaded. This prevents long counts on the first load.

# Registers

The controller has a number of accessible registers. The system programmer may gain access to or control any of the controller registers through the system microprocessor. These registers are used to control the controller operations and to transmit and receive data.

Specific registers are selected according to the following figure:

| DLAB<br>State * | Port<br>Address<br>(hex) | R/W | Register                          |

|-----------------|--------------------------|-----|-----------------------------------|

| 0               | 0nF8 **                  | w   | Transmitter Holding Register n    |

| 0               | 0nF8 **                  | Ŕ   | Receiver Buffer Register n        |

| 1               | 0nF8 **                  | R/W | Divisor Latch, Low Byte           |

| 1               | 0nF9 **                  | R/W | Divisor Latch, High Byte          |

| 0               | 0nF9 **                  | R/W | Interrupt Enable Register         |

| X               | 0nFA **                  | R   | Interrupt Identification Register |

| X               | 0nFA **                  | W   | FIFO Control Register             |

| X               | 0nFB **                  | R/W | Line Control Register             |

| Х               | 0nFC **                  | R/W | Modem Control Register            |

| Х               | 0nFD **                  | R   | Line Status Register              |

| X               | OnFE **                  | R   | Modem Status Register             |

| X               | OnFF **                  | R/W | Scratch Register                  |

Figure 4-165. Serial Port Register Addresses

# Transmitter Holding Register (hex nF8)

The Transmitter Holding register contains the character to be sent. Bit 0 is the least-significant bit and the first bit sent serially as shown in the following figure:

| Bit | Function   |  |

|-----|------------|--|

| 7   | Data Bit 7 |  |

| 6   | Data Bit 6 |  |

| 5   | Data Bit 5 |  |

| 4   | Data Bit 4 |  |

| 3   | Data Bit 3 |  |

| 2   | Data Bit 2 |  |

| 1   | Data Bit 1 |  |

| Ó   | Data Bit 0 |  |

Figure 4-166. Transmitter Holding Register (THR)

# Receiver Buffer Register (hex nF8)

The Receiver Buffer register (RBR) contains the received character. Bit 0 is the least-significant bit and the first bit received serially as shown in the following figure:

| Bit | Function   |  |

|-----|------------|--|

| 7   | Data Bit 7 |  |

| 6   | Data Bit 6 |  |

| 5   | Data Bit 5 |  |

| 4   | Data Bit 4 |  |

| 3   | Data Bit 3 |  |

| 2   | Data Bit 2 |  |

| 1   | Data Bit 1 |  |

| 0   | Data Bit 0 |  |

Figure 4-167. Receiver Buffer Register (RBR)

### Divisor Latch Register LSB (hex nF8)

| Bit | Function |  |

|-----|----------|--|

| 7   | Bit 7    |  |

| 6   | Bit 6    |  |

| 5   | Bit 5    |  |

| 4   | Bit 4    |  |

| 3   | Bit 3    |  |

| 2   | Bit 2    |  |

| 1   | Bit 1    |  |

| 0   | Bit 0    |  |

Figure 4-168. Divisor Latch Register (LSB)

# Divisor Latch Register MSB (hex nF9)

| Bit | Function |  |

|-----|----------|--|

| 7   | Bit 7    |  |

| 6   | Bit 6    |  |

| 5   | Bit 5    |  |

| 4   | Bit 4    |  |

| 3   | Bit 3    |  |

| 2   | Bit 2    |  |

| 1   | Bit 1    |  |

| 0   | Bit 0    |  |

Figure 4-169. Divisor Latch Register (MSB)

The Divisor Latch registers are used to program the baud rate generator. The values in these two registers form the divisor of the clock input (1.8432 MHz), which establishes the desired baud rate.

The following figure illustrates the use of the baud-rate generator with a frequency of 1.8432 MHz. For baud rates of 19,200 and below, the error obtained is minimal.

Note: In no case should the data speed be greater than 19,200 baud.

| Desired<br>Baud | Divisor Use<br>Generate 1 | 6x Clock | Percent of Error<br>Difference Between |  |

|-----------------|---------------------------|----------|----------------------------------------|--|

| Rate            | (Decimal)                 | (Hex)    | Desired and Actual                     |  |

| 50              | 2304                      | 0900     |                                        |  |

| 75              | 1536                      | 0600     |                                        |  |

| 110             | 1047                      | 0417     | 0.026                                  |  |

| 134.5           | 857                       | 0359     | 0.058                                  |  |

| 150             | 768                       | 0300     |                                        |  |

| 300             | 384                       | 0180     |                                        |  |

| 600             | 192                       | 00C0     | <b></b>                                |  |

| 1200            | 96                        | 0060     |                                        |  |

| 1800            | 64                        | 0040     |                                        |  |

| 2000            | 58                        | 003A     | 0.69                                   |  |

| 2400            | 48                        | 0030     | <del></del>                            |  |

| 3600            | 32                        | 0020     |                                        |  |

| 4800            | 24                        | 0018     |                                        |  |

| 7200            | 16                        | 0010     | <del></del>                            |  |

| 9600            | 12                        | 000C     | un.                                    |  |

| 19200           | 6                         | 0006     |                                        |  |

Figure 4-170. Baud Rates at 1.8432 MHz

# Interrupt Enable Register (hex nF9)

This 8-bit register allows the four types of controller interrupts to separately activate the 'chip-interrupt' output signal. The interrupt system can be totally disabled by clearing bits 0 through 3 of the Interrupt Enable register. Similarly, by setting the appropriate bits of this register to 1, selected interrupts can be enabled. Disabling the interrupts inhibits the 'chip-interrupt' output signal from the controller. All other system functions operate normally, including the setting of the Line Status and Modem Status registers.

| Bit   | Function                                     |

|-------|----------------------------------------------|

| 7 - 4 | Reserved = 0                                 |

| 3     | Modem-Status Interrupt                       |

| 2     | Receiver-Line-Status Interrupt               |

| 1     | Transmitter-Holding-Register-Empty Interrupt |

| 0     | Received Data Available Interrupt            |

Figure 4-171. Interrupt Enable Register

Bits 7 - 4 Reserved. These bits are always cleared to 0.

- Bit 3 When set to 1, this bit enables the modem-status interrupt.

- Bit 2 When set to 1, this bit enables the receiver-line-status interrupt.

- Bit 1 When set to 1, this bit enables the transmitter-holding-register-empty interrupt.

- Bit 0 When set to 1, this bit enables the received-data-available interrupt.

## Interrupt Identification Register (hex nFA)

In order to minimize programming overhead during data character transfers, the controller prioritizes interrupts into four levels:

- Priority 1 Receiver-line-status

- Priority 2 Received-data-available

- Priority 3 Transmitter-holding-register-empty

- Priority 4 Modem status.

Information about a pending interrupt is stored in the Interrupt Identification register. When the Interrupt Identification register is addressed, the pending interrupt with the highest priority is held and no other interrupts are acknowledged until the system microprocessor services that interrupt.

| Bit   | Function              | ! |

|-------|-----------------------|---|

| 7 - 3 | Reserved = 0          |   |

| 2     | Interrupt ID, Bit 1   |   |

| 1     | Interrupt ID, Bit 0   |   |

| 0     | Interrupt Pending = 0 |   |

Figure 4-172. Interrupt Identification Register

- Bits 7 3 Reserved. These bits are always cleared to 0.

- Bits 2, 1 These two bits identify the pending interrupt with the highest priority, as shown in Figure 4-173 on page 4-162.

- When this bit is set to 1, no interrupt is pending, and polling (if used) continues. When this bit is cleared to 0, an interrupt is pending, and the contents of this register can be used as a pointer to the appropriate interrupt service routine.

This bit can be used in either hard-wired, prioritized, or polled conditions to indicate if an interrupt is pending.

Bits 2 - 0 select Interrupt Control Functions as shown in the following figure:

| Bits<br>2 1 0 | Priority | Туре                                        | Cause                                                         | Interrupt Reset<br>Control                                                               |

|---------------|----------|---------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 001           | -        | None                                        | None                                                          | -                                                                                        |

| 110           | Highest  | Receiver<br>Line Status                     | Overrun, Parity,<br>or Framing Error<br>or Break<br>Interrupt | Read the Line Status<br>Register                                                         |

| 100           | Second   | Received<br>Data<br>Available               | Data in Receiver<br>Buffer                                    | Read the Receiver Buffer<br>Register                                                     |

| 010           | Third    | Transmitter<br>Holding<br>Register<br>Empty | Transmitter<br>Holding Register<br>is Empty                   | Read Interrupt<br>Identification register or<br>Write to Transmitter<br>Holding Register |

| 000           | Fourth   | Modem<br>Status                             | Change in signal<br>status from<br>modem                      | Read the Modem Status<br>Register                                                        |

Figure 4-173. Interrupt Control Functions

## Line Control Register (hex nFB)

The format of asynchronous communications is programmed through the Line Control register.

| Bit | Function                  |  |

|-----|---------------------------|--|

| 7   | Divisor Latch Access Bit  |  |

| 6   | Set Break                 |  |

| 5   | Stick Parity              |  |

| 4   | Even Parity Select        |  |

| 3   | Parity Enable             |  |

| 2   | Number of Stop Bits       |  |

| 1   | Word Length Select, Bit 1 |  |

| Ò   | Word Length Select, Bit 0 |  |

Figure 4-174. Line Control Register (LCR)

- Bit 7 This bit must be set to 1 during a read or write operation to gain access to the divisor latches of the baud-rate generator. It must be cleared to 0 to gain access to the Receiver Buffer, Transmitter Holding, or Interrupt Enable registers.

- Bit 6 When this bit is set to 1 set-break is enabled, serial output is forced to the spacing state and remains there regardless of other transmitter activity. When this bit is cleared to 0, set-break is disabled.

- Bit 5 When bits 5, 4, and 3 are set to 1, the parity bit is sent and checked as a logical 0. When bits 5 and 3 are set to 1, and bit 4 is cleared to 0, the parity bit is sent and checked as a logical 1.

- Bit 4 When this bit and bit 3 are set to 1, an even number of logical ones are transmitted and checked in the data word bits and parity bit. When this bit is cleared to 0, and bit 3 is set to 1, an odd number of logical ones are transmitted and checked in the data word bits and parity bit.

- Bit 3 When set to 1, a parity bit is generated (transmit data) or checked (receive data) between the last data word bit and stop bit. (The parity bit is used to produce an even or odd number of ones when the data-word bits and the parity bit are summed.)

- Bit 2 This bit, along with bits 0 and 1, specifies the number of stop bits in each serial character that is sent or received as shown in the following figure:

| Bit 2 | Word<br>Length * | Number of<br>Stop Bits |  |

|-------|------------------|------------------------|--|

| 0     | N/A              | 1                      |  |

| 1     | 5-Bits           | 1-1/2                  |  |

| 1     | 6-Bits           | 2                      |  |

| 1     | 7-Bits           | 2                      |  |

| 1     | 8-Bits           | 2                      |  |

Figure 4-175. Stop Bits

Bits 1, 0 These two bits specify the number of bits in each serial character that is sent or received. Word length is selected as shown in the following figure:

| Bit<br>1 0 | Word Length |  |

|------------|-------------|--|

| 00         | 5-Bits      |  |

| 0.1        | 6-Bits      |  |

| 10         | 7-Bits      |  |

| 11         | 8-Bits      |  |

Figure 4-176. Word Length

### Modem Control Register (hex nFC)

This 8-bit register controls the data exchange with the modem, data set, or peripheral device emulating a modem.

| Bit   | Function            |  |

|-------|---------------------|--|

| 7 - 5 | Reserved = 0        |  |

| 4     | Loop                |  |

| 3     | Out 2               |  |

| 2     | Out 1               |  |

| 1     | Request-to-Send     |  |

| 0     | Data-Terminal-Ready |  |

Figure 4-177. Modem Control Register (MCR)

- Bits 7 5 Reserved. These bits are always cleared to 0.

- Bit 4 This bit provides a loopback feature for diagnostic testing of the serial port. When bit 4 is set to 1:

- Transmitter-serial-output is set to the marking state.

- Receiver-serial-input is disconnected.

- Output of the Transmitter Shift register is "looped back" to the Receiver Shift register input.

Note: The Transmitter and Receiver Shift registers are not accessible NS16550 registers.

- The modem control inputs (CTS, DSR, DCD, and RI) are disconnected.

- The modem control outputs (DTR, RTS, OUT 1, and OUT 2) are internally connected to the four modem control inputs.

- The modem control output pins are forced inactive.

When the serial port is in the diagnostic mode, transmitted data is immediately received. This feature allows the

system microprocessor to verify the transmit-data and receive-data paths of the serial port.

When the serial port is in the diagnostic mode, the receiver and transmitter interrupts are fully operational. The modem control interrupts are also operational, but their sources are the lower four bits of the Modem Control register instead of the four modem control input signals. The interrupts are still controlled by the Interrupt Enable register.

- Bit 3 This bit controls the 'output 2' (OUT 2) signal which is an auxiliary user-designated interrupt enable signal. OUT 2 is used to control the interrupt signal to the channel. Setting this bit to 1 enables the interrupt. Clearing this bit to 0 disables the interrupt.

- This bit controls the 'output 1' (OUT 1) signal which is an auxiliary user-designated output signal. When set to 1, OUT 1 is forced active. When cleared to 0, OUT 1 is forced inactive.

- Bit 1 This bit controls the 'request-to-send' (RTS) modem control output signal. When set to 1, RTS is forced active. When cleared to 0, RTS is forced inactive.

- Bit 0 This bit controls the 'data-terminal-ready' (DTR) modem control output signal. When set to 1, DTR is forced active. When cleared to 0, DTR is forced inactive.

### Line Status Register (hex nFD)

This 8-bit register provides the system microprocessor with status information about the data transfer.

| Bit | Function                                  |

|-----|-------------------------------------------|

| 7   | Reserved = 0                              |

| 6   | Transmitter Shift Register Empty (TEMT)   |

| 5   | Transmitter Holding Register Empty (THRE) |

| 4   | Break Interrupt (BI)                      |

| 3   | Framing Error (FE)                        |

| 2   | Parity Error (PE)                         |

| 1   | Overrun Error (OR)                        |

| 0   | Data Ready (DR)                           |

Figure 4-178. Line Status Register (LSR)

- Bit 7 Reserved. This bit is always cleared to 0.

- Bit 6 This bit is set to 1 when the Transmitter Holding register and the Transmitter Shift register are both empty. It is cleared to 0 when either the Transmitter Holding register or the Transmitter Shift register contains a data character.

- Bit 5 This bit indicates that the serial port controller is ready to accept a new character for transmission. This bit is set to 1 when a character is transferred from the Transmitter Holding register into the Transmitter Shift register. This bit is cleared to 0 when the system microprocessor loads the Transmitter Holding register.

This bit also causes the controller to issue an interrupt to the system microprocessor when bit 1 in the Interrupt Enable register is set to 1.

Bit 4 This bit is set to 1 when the received data input is held in the spacing state for longer than a fullword transmission time (that is, the total time of start bit + data bits + parity + stop bits).

**Note:** Bits 1 through 4 are the error conditions that produce a receiver line-status interrupt whenever any of the corresponding conditions are detected.

Bit 3 This bit is set to 1 when the stop bit, following the last data bit or parity bit, is at a spacing level. This indicates that the received character did not have a valid stop bit.

- Bit 2 This bit is set to 1 when a parity error is detected (the received character does not have the correct even or odd parity, as selected by the even-parity-select bit). This bit is cleared to 0 when the system microprocessor reads the contents of the Line Status register.

- Bit 1 When set to 1, this bit indicates that data in the Receiver Buffer register was not read by the system microprocessor before the next character was transferred into the Receiver Buffer register, destroying the previous character. This bit is cleared to 0 when the system microprocessor reads the contents of the Line Status register.

- Bit 0 This bit is set to 1 when a complete incoming character has been received and transferred into the Receiver Buffer register. This bit is cleared to 0 by reading the Receiver Buffer register.

### Modem Status Register (hex nFE)

This 8-bit register provides the current state of the control lines from the modem (or external device) to the system microprocessor. In addition, bits 3 through 0 of this register provide change information. These four bits are set to logical 1 whenever a control input from the modem changes state. They are reset to logical 0 whenever the system microprocessor reads this register.

| Bit | Function                     |  |

|-----|------------------------------|--|

| 7   | Data-Carrier-Detect          |  |

| 6   | Ring Indicator               |  |

| 5   | Data-Set-Ready               |  |

| 4   | Clear-to-Send                |  |

| 3   | Delta-Data-Carrier-Detect    |  |

| 2   | Trailing Edge Ring Indicator |  |

| 1   | Delta-Data-Set-Ready         |  |

| 0   | Delta-Clear-to-Send          |  |

Figure 4-179. Modem Status Register (MSR)

Bit 7 This bit is the inverted 'data-carrier-detect' modem control input signal. If bit 4 of the Modem Control register is set to 1, this bit is equivalent to bit 3 in the Modem Control register.

- Bit 6 This bit is the inverted 'ring-indicator' modem control input signal. If bit 4 of the Modem Control register is set to 1, this bit is equivalent to bit 2 in the Modem Control register.

- Bit 5 This bit is the inverted 'data-set-ready' modem control input signal. If bit 4 of the Modem Control register is set to 1, this bit is equivalent to bit 0 in the Modem Control register.

- Bit 4 This bit is the inverted 'clear-to-send' modem control input signal. If bit 4 of the Modem Control register is set to 1, this bit is equivalent to bit 1 in the Modem Control register.

- When set to 1, this bit indicates that the 'data-carrier-detect' modem control input signal has changed state since the last time it was read by the system microprocessor.

**Note:** Whenever bit 0, 1, 2, or 3 is set to 1, a modem status interrupt is generated.

- When set to 1, this bit indicates that the 'ring-indicator' modem control input signal has changed from an active condition to an inactive condition.

- Bit 1 When set to 1, this bit indicates that the 'data-set-ready' modem control input signal has changed state since the last time it was read by the system microprocessor.

- When set to 1, this bit indicates that the 'clear-to-send' modem control input signal has changed state since the last time it was read by the system microprocessor.

## Scratch Register

This register does not control the serial port in any way. It can be used by the system microprocessor to temporarily hold data.

# **Serial Port Controller Programming Considerations**

The serial port uses the NS16550 serial communications controller. The NS16550 is functionally compatible with the NS16450 and appears identical to software as the IBM Personal Computer AT serial port on the serial/parallel adapter. See "Hardware Interrupts" on page 9-6 for additional programming considerations.

The serial port can be configured to either Serial 1 or Serial 2 using the system configuration utilities.

## Signal Descriptions

### **Modem Control Input Signals**

The following are input signals from the modem or external device to the controller. Bits 7 through 4 in the Modem Status register indicate the condition of these signals. Bits 3 through 0 in the Modem Status register monitor these signals to indicate when the modem changes state.

Clear to Send (CTS): When active, this signal indicates that the modem is ready for the serial port to transmit data.

**Data Set Ready (DSR):** When active, this signal indicates the modem or data set is ready to establish the communications link and transfer data with the controller.

**Ring Indicator (RI):** When active, this signal indicates the modem or data set detected a telephone ringing signal.

Data Carrier Detect (DCD): When active, this signal indicates that the modem or data set detected a data carrier.

## **Modem Control Output Signals**

The following are controller output signals. They are all set inactive upon a master reset operation. These signals are controlled by bits 3 through 0 in the Modem Control register.

**Data Terminal Ready (DTR):** When active, this signal informs the modem or data set that the controller is ready to communicate.

Request to Send (RTS): When active, this signal informs the modem or data set that the controller is ready to send data.

Output 1 (OUT 1): This signal is pulled high.

**Output 2 (OUT 2):** User-designated output. This signal controls interrupts to the system.

## Voltage Interchange Information

The signal is considered in the *marking* condition when the voltage on the interchange circuit, measured at the interface point, is more negative than -3 Vdc with respect to signal ground. The signal is considered in the *spacing* condition when the voltage is more positive than +3 Vdc with respect to signal ground. The region between +3 Vdc and -3 Vdc is defined as the transition region, and considered an invalid level. The voltage that is more negative than -15 Vdc or more positive than +15 Vdc is also considered an invalid level.

| Interchange<br>Voltage | Binary State | Signal Condition | Interface<br>Control Function |  |

|------------------------|--------------|------------------|-------------------------------|--|

| Positive Voltage       | Binary 0     | Spacing          | On                            |  |

| Negative Voltage       | Binary 1     | Marking          | Off                           |  |

Figure 4-180. Voltage Levels

### Connector

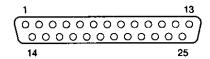

The interface uses the standard D-shell connector and pin assignments defined for RS-232-C. The voltage levels are EIA only. Current loop interface is not supported.

The following figure shows the pin assignments for the serial port in a communications environment.

Figure 4-181. Serial Port Connector

| Pin No. | I/O | Signal Name         | Pin No. | 1/0 | Signal Name            |

|---------|-----|---------------------|---------|-----|------------------------|

| 1       | NA  | Not Connected       | 14      | NA  | Not Connected          |

| 2       | 0   | Transmit Data       | 15      | NA  | Not Connected          |

| 3       | 1   | Receive Data        | 16      | NA  | Not Connected          |

| 4       | 0   | Request to Send     | 17      | NA  | Not Connected          |

| 5       | l l | Clear to Send       | 18      | NA  | Not Connected          |

| 6       | )   | Data Set Ready      | 19      | NA  | Not Connected          |

| 7       | NA  | Signal Ground       | 20      | 0   | Data Terminal<br>Ready |

| 8       | 1   | Data Carrier Detect | 21      | NA  | Not Connected          |

| 9       | NA  | Not Connected       | 22      | 1   | Ring Indicate          |

| 10      | NA  | Not Connected       | 23      | NA  | Not Connected          |

| 11      | NA  | Not Connected       | 24      | NA  | Not Connected          |

| 12      | NA  | Not Connected       | 25      | NA  | Not Connected          |

| 13      | NA  | Not Connected       |         |     |                        |

Figure 4-182. Serial Port Connector Signal and Voltage Assignments

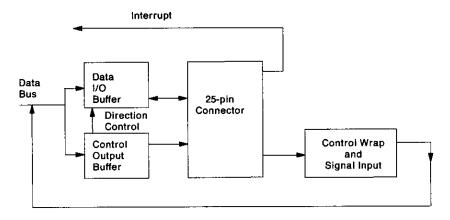

### **Parallel Port Controller**

The parallel port allows the attachment of various devices that transfer 8 bits of parallel data at standard TTL levels. It has a 25-pin, D-shell connector. This port may be addressed as parallel port 1, 2, or 3.

The parallel port is designed to be compatible with previous IBM Personal Computer parallel port implementations. The primary function of the parallel port is to attach a printer with a parallel interface to the system. The parallel port has an extended mode that allows support of bidirectional input and output. The port also supports level sensitive interrupts and a readable interrupt pending status.

The following figure is a block diagram of the parallel port controller.

Figure 4-183. Parallel Port Controller Block Diagram

## **Parallel Port Programmable Option Select**

The parallel port can be configured to three different address spaces previously used in IBM Personal Computer products. These addresses are selected by placing the system board in Setup (see "Programmable Option Select" on page 2-21) and performing an I/O write to port hex 0102. Bits 6 and 5 in port hex 0102 are used to select the address spaces shown below.

| Bit 6 | Bit 5 | Function   |

|-------|-------|------------|

| 0     | 0     | Parallel 1 |

| 0     | 1     | Parallel 2 |

| 1     | 0     | Parallel 3 |

Figure 4-184. Parallel Port Configuration

The address assignments for each configuration are shown in the following figure.

|            | Data Address<br>(hex) | Status Address<br>(hex) | Parallel Control Address<br>(hex) |