**AP-358**

### APPLICATION NOTE

### **Intel 82077SL for Super Dense Floppies**

**KATEN A. SHAH** APPLICATION ENGINEER

September 1992

Order Number: 292093-002

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

\*Other brands and names are the property of their respective owners.

†Since publication of documents referenced in this document, registration of the Pentium, OverDrive and iCOMP trademarks has been issued to Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

COPYRIGHT © INTEL CORPORATION, 1996

### Intel 82077SL for Super Dense Floppies

| <b>CONTENTS</b> PAGE                            | <b>CONTENTS</b> PAGE                           |

|-------------------------------------------------|------------------------------------------------|

| <b>INTRODUCTION</b> 1                           | 82077AA/SL'S PERPENDICULAR<br>MODE SUPPORT     |

| PURPOSE 1                                       |                                                |

| PERPENDICULAR RECORDING<br>MODE1                | PROGRAMMING PERPENDICULAR<br>MODE6             |

| PERPENDICULAR DRIVE FORMAT<br>AND SPECIFICATION | INTERFACE BETWEEN 82077AA/SL<br>AND THE DRIVE9 |

| PERPENDICULAR MODE<br>COMMAND                   | 82077SL 4 MB DESIGN 14                         |

#### INTRODUCTION

The evolution of the floppy has been marked in little over a decade by a significant increase in capacity accompanied by a noticeable decrease in the form factor from the early 8 inch floppy disks to the present day 3.5 inch floppy disks. This decade will also be remarkable as OEMs adopt "Super" dense floppies.

The most commonly seen floppies today are invariably one of the form factors – the 5.25" or the 3.5". Each form factor has several associated capacity ranges. The 5.25" floppies available are: 180 KB (single density), 360 KB (double density) and 1.2 MB (high density). The 3.5" floppies available are: 720 KB (double density) and 1.44 MB (high density). The emerging super dense floppies will evolve on the installed base of 3.5" floppies. The latest member of this set is the 2.88 MB (extra density) floppy, pioneered by Toshiba. The cornerstone of market acceptance of newer drives is compatibility to the older family. The 2.88 MB (formatted) floppy drive allows the user to format, read from and write to the lower density diskettes.

As programs and data files get bigger, the demand for higher capacity floppies becomes obvious. There are several 3.5" higher density drives available from various vendors with capacities well into the 20 MB range. NEC has introduced a 13 MB drive and companies such as Insite have introduced 20 MB drives. Both drives require servo-mechanisms to accurately position the head over the right track. NEC's drive has the standard floppy drive interface whereas Insite's interface is SCSI based. The market for these floppy drives will remain a niche unless they receive more OEM support.

Initiated by Toshiba's research and innovation of the higher density 4 MB floppy disk media, the market is headed towards the super dense floppy drive. After IBM's endorsement of the 4 MB (unformatted) floppy disk drives on their PS/2 model 57 and PS/2 model 90, several OEMs have shown a growing interest in "super" dense floppy disk drives. The latest DOS 5.0 supports the new 4 MB floppy media and BIOS vendors like Pheonix, AMI, Award, Quadtel, System Soft, and Microid all support the newer 4 MB floppy media.

#### PURPOSE

An important consideration to implement the 4 MB floppy drive is the floppy disk controller. Intel's highly integrated floppy disk controller, 82077AA/SL, has led the market in supporting the 4 MB floppy drive. Two ingredients are necessary to fully support these drives: 1 Mbps transfer rate and the perpendicular recording mode. This paper deals with a discussion of what the perpendicular mode is and how can a 4 MB floppy disk drive be implemented in a system using the 82077AA/SL.

#### PERPENDICULAR RECORDING MODE

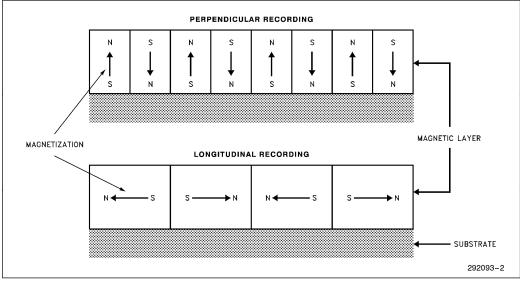

Toshiba has taken the 2 MB floppy and doubled the storage capacity by doubling the number of bits per track. Toshiba achieved this by an innovative magnetic recording mode, called the vertical or the perpendicular recording mode. This mode utilizes magnetization perpendicular to the recording medium plane. This is in contrast to the current mode of longitudinal recording plane. By making the bits stand vertical as opposed to on their side, recording density is effectively doubled, Figure 1. The new perpendicular mode of recording not only produces sharp magnetization transitions necessary at higher recording densities, but is also more stable.

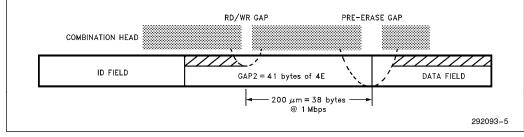

The 4 MB disks utilize barium ferrite coated substrates to achieve perpendicular mode of magnetization. Current disks use cobalt iron oxide (Co-g-Fe<sub>2</sub>O<sub>3</sub>) coating for longitudinal recording. The barium ferrite ensures good head to medium contact, stable output and durability in terms of long use. High coercivity is required to attain high recording density for a longitudinal recording medium (coercivity specification of a disk refers to the magnetic field strength required to make an accurate record on the disk). A conventional head could not be used in this case; however, the barium ferrite disk has low coercivity and the conventional ferrite head can be used. The new combination heads include a pre-erase mechanism, i.e., the ferrite ring heads containing erase elements followed by the read/write head. These erase elements have deep overwrite penetration and ensure complete erasure for writing new data. The distance between the erase elements and the read/write head is about 200mm. This distance is important from the floppy disk controller point of view and will be discussed in later sections.

Figure 1. Perpendicular vs Longitudinal Recording

#### PERPENDICULAR DRIVE FORMAT AND SPECIFICATION

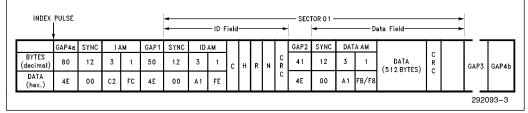

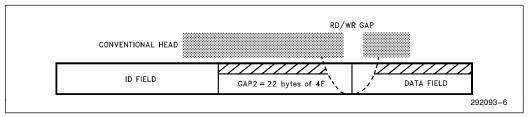

Figures 2a and 2b show the IBM drive format for both double density and perpendicular modes of recording. The main difference in recording format is the length of Gap2 between the ID field and the Data field. The main reason for the increased Gap2 length is the preerase head preceding the read/write head on the newer 4 MB floppy drives. The size of the data field is main-tained at 512 KBytes standard. The increase in the capacity is implemented by increasing the number of sectors from 18 to 36. Table 1 shows the specifications of the various capacity 3.5" drives.

#### PERPENDICULAR MODE COMMAND

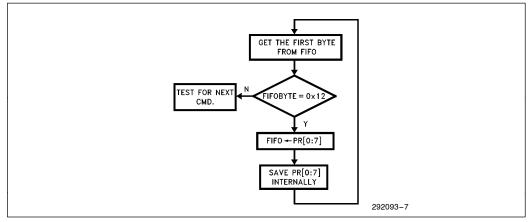

The current 82077AA/SL parts contain the "enhanced" perpendicular mode command as shown in Figure 3. This is a two byte command with the first byte being the command code (0x12H). The 2nd byte contains the parameters required to enable perpendicular mode recording. The former command (in the older 82077 parts) included only the WGATE and GAP bits. This command is compatible to the older mode where only the two LSBs are written. The enhanced mode allows system designers to designate specific drives as perpendicular recording drives. The second byte will be referenced as the PR[0:7] byte for ease of discussion. The following discusses the use of the enhanced perpendicular recording mode.

Figure 2a. Conventional IBM 1 MB and 2 MB Format (MFM)

| INDEX              | PULSE |      |     |    |      | •    |     | — ID F | ield |   |   |   | •      | — SEC | TOR 01 - |     | Da    | ata Field           |        |      |      |

|--------------------|-------|------|-----|----|------|------|-----|--------|------|---|---|---|--------|-------|----------|-----|-------|---------------------|--------|------|------|

|                    | GAP4a | SYNC | I A | M  | GAP1 | SYNC | ID  | AM     |      |   |   |   |        | GAP2  | SYNC     | DAT | A AM  |                     |        |      |      |

| BYTES<br>(decimal) | 80    | 12   | 3   | 1  | 50   | 12   | 3   | 1      | с    | н | R | N | C<br>R | 41    | 12       | 3   | 1     | DATA<br>(512 BYTES) | C<br>R | GAP3 | GAP4 |

| DATA<br>(hex.)     | 4E    | 00   | C2  | FC | 4E   | 00   | A 1 | FE     | 1    |   |   |   | С      | 4E    | 00       | A 1 | FB/F8 | . ,                 | C      |      |      |

Figure 2b. Perpendicular 4 MB Format (MFM)

| Dhase   | Phase R/W Data Bus         |         |        |         |         |         |         |          |            | Bomorko            |  |

|---------|----------------------------|---------|--------|---------|---------|---------|---------|----------|------------|--------------------|--|

| Fliase  | n/ w                       | D7      | D6     | D5      | D4      | D3      | D2      | D1       | D0         | Remarks            |  |

|         | PERPENDICULAR MODE COMMAND |         |        |         |         |         |         |          |            |                    |  |

| Command | W<br>W                     | 0<br>OW | 0<br>0 | 0<br>D3 | 1<br>D2 | 0<br>D1 | 0<br>D0 | 1<br>GAP | 0<br>WGATE | Command Code<br>PR |  |

Figure 3. Perpendicular Mode Command

| Table 1. Specifications of TDDs                         |          |                 |                 |                |                 |                 |  |  |  |  |  |  |

|---------------------------------------------------------|----------|-----------------|-----------------|----------------|-----------------|-----------------|--|--|--|--|--|--|

| Various Parameters Used<br>in the Different Kinds of FD | -        | 5.25″<br>360 KB | 5.25″<br>1.2 MB | 3.5″<br>720 KB | 3.5″<br>1.44 MB | 3.5″<br>2.88 MB |  |  |  |  |  |  |

| Number of Cylinders                                     |          | 40              | 80              | 80             | 80              | 80              |  |  |  |  |  |  |

| Sectors/Track                                           |          | 9               | 15              | 9              | 18              | 36              |  |  |  |  |  |  |

| Formatted Capacity                                      |          | 354 KB          | 1.2 MB          | 720 KB         | 1.44 MB         | 2.88MB          |  |  |  |  |  |  |

| Unformatted Capacity                                    |          | 360 KB          | 1.6 MB          | 1 MB           | 2 MB            | 4 MB            |  |  |  |  |  |  |

| Rotation Speed (rpm)                                    | XT<br>AT | 300<br>360      | 360             | 300            | 300             | 300             |  |  |  |  |  |  |

| Track Density (tpi)                                     |          | 48              | 96              | 135            | 135             | 135             |  |  |  |  |  |  |

| Recording Density (bpi)                                 |          | 5876            | 9870            | 8717           | 17432           | 34868           |  |  |  |  |  |  |

| Data Transfer Rate (Mbps)                               | XT<br>AT | 0.25<br>0.30    | 0.5             | 0.25           | 0.5             | 1               |  |  |  |  |  |  |

| Gap Length for Read/Write                               |          | 42              | 42              | 27             | 27              | 56              |  |  |  |  |  |  |

| Gap Length for Format                                   |          | 80              | 80              | 84             | 84              | 83              |  |  |  |  |  |  |

| Sector Size                                             |          | 512 KB          | 512 KB          | 512 KB         | 512 KB          | 512 KB          |  |  |  |  |  |  |

| Density Notation                                        |          | DD/DS           | HD/DS           | DD/DS          | HD/DS           | ED/DS           |  |  |  |  |  |  |

#### Table 1. Specifications of FDDs

The following describes the various functions of the programmed bits in the PR:

- OW If this bit is not set high, all PR[2:5] are ignored. In other words, if OW = 0, only GAP and WGATE are considered. In order to select a drive as perpendicular, it is necessary to set OW = 1 and select the Dn bit.

- Dn This refers to the drive specification bits and corresponds to PR[2:5]. These bits are considered only if OW = 1. During the READ/ WRITE/FORMAT command, the drive selected in these commands is compared to Dn. If the bits match then perpendicular mode will be enabled for that drive. For example, if D0 is set then drive 0 will be configured for perpendicular mode.

- GAP This alters the Gap2 length as required by the perpendicular mode format.

- WGATE Write gate alters timing of WE to allow for pre-erase loads in perpendicular drives.

The VCOEN timing and the length of the Gap2 field (explained above) can be altered to accommodate the

unique requirements of the 4 MB floppy drives by GAP and WGATE bits of the PR. Table 2 describes the effects of the GAP and WGATE bits for the perpendicular command.

#### 82077AA/SL's PERPENDICULAR MODE SUPPORT

The 82077AA and 82077SL both support 4 MB recording mode. The 82077SL has power management features included as well. Both AA and SL product lines have three versions each out of which two of the versions support the 4 MB floppy drives. The 82077AA-1, 82077AA, 82077SL, and 82077SL-1 all support the 4 MB floppy drives. A single command puts the 82077AA/SL into the perpendicular mode. This mode also requires the data rate to be set at 1 Mbps. The FIFO that is unique to Intel's 82077AA/SL parts may become necessary to remove the host interface bottleneck due to the higher data rate. The 4 MB floppy disk drives are downward compatible to 1 MB and 2 MB floppy diskettes. The following discussion explains the implications of the new 4 MB combination head and the functionality of the perpendicular mode command.

| GAP | WGATE | Mode                                    | VCO Low<br>Time after<br>Index Pulse | Length<br>of Gap2<br>Format<br>Field | Portion<br>of Gap2<br>Written by<br>Write Data<br>Operation | Gap2 VCO<br>Low Time<br>for Read<br>Operations |

|-----|-------|-----------------------------------------|--------------------------------------|--------------------------------------|-------------------------------------------------------------|------------------------------------------------|

| 0   | 0     | Conventional                            | 33 Bytes                             | 22 Bytes                             | 0 Bytes                                                     | 24 Bytes                                       |

| 0   | 1     | Perpendicular<br>(Data Rate = 500 kbps) | 33 Bytes                             | 22 Bytes                             | 19 Bytes                                                    | 24 Bytes                                       |

| 1   | 0     | Conventional                            | 33 Bytes                             | 22 Bytes                             | 0 Bytes                                                     | 24 Bytes                                       |

| 1   | 1     | Perpendicular                           | 33 Bytes                             | 41 Bytes                             | 38 Bytes                                                    | 43 Bytes                                       |

#### Table 2. Effects of GAP and WGATE Bits

The implementation of 4 MB drives requires understanding the Gap2 (see Figures 2a and 2b) and VCO timing requirements unique to these drives. These new requirements are dictated by the design of the "combination head" in these drives. Rewriting of disks in the 4 MB drives requires a pre-erase gap to erase the magnetic flux on the disk preceding the writing by the read/write gap. The read/write gap in the 4 MB drive does not have sufficient penetration (as shown in Figure 4a) to overwrite the existing data. In the conventional drives, the read/write gap had sufficient depth and could effectively overwrite the older data as depicted in Figure 4b. It must be noted that it is necessary to write the conventional 2 MB media in the 4 MB drive at 500 Kbps perpendicular mode. This ensures proper erasure of existing data and reliable write of the new data. The pre-erase gap in the 4 MB floppy drives is activated only during format and write commands. Both the pre-erase gap and read/write gap are activated at the same time.

As shown in Figure 4a, the pre-erase gap precedes the read/write gap by 200mm. This distance translated to bytes is about 38 bytes at a data rate of 1 Mbps and 19 bytes at 500 Kbps. Whenever the read/write gap is enabled by the Write Gate signal the pre-erase gap is activated at the same time.

Figure 4a. Head Design for the 4 MB Perpendicular Mode

Figure 4b. Head Design for the Conventional 2 MB Mode

In conventional drives, the Write Gate is asserted at the beginning of the sync field, i.e., when the read/write is at the beginning of the data field. The controller then writes the new sync field, data address mark, data field and CRC (see Figure 2a). With the combination head, the read/write gap must be activated in the Gap2 field to ensure proper write of the new sync field. To accommodate both the distance between the pre-erase gap and read/write gap and the head activation and deactivation time, the Gap2 field is expanded to a length of 41 bytes at 1 Mbps (see Figure 2b). Since the bit density is proportional to the data rate, 19 bytes will be written in the Gap2 field at 500 Kbps data rate in the perpendicular mode.

On the read back by the 82077AA/SL, the controller must begin the synchronization at the beginning of the sync field. For conventional mode, the internal PLL VCO is enabled (VCOEN) approximately 24 bytes from the start of the Gap2 field. However, at 1 Mbps perpendicular mode the VCOEN goes active after 43 bytes to accomodate the increased Gap2 field size. For each case, a 2 byte cushion is maintained from the beginning of the sync field to avoid write splices caused by motor speed variation.

It should be noted that none of the alterations in Gap2 size, VCO timing or Write Gate timing affect the nor-

mal program flow. Once the perpendicular command is invoked, 82077AA/SL behaviour from the user standpoint is unchanged.

### PROGRAMMING PERPENDICULAR MODE

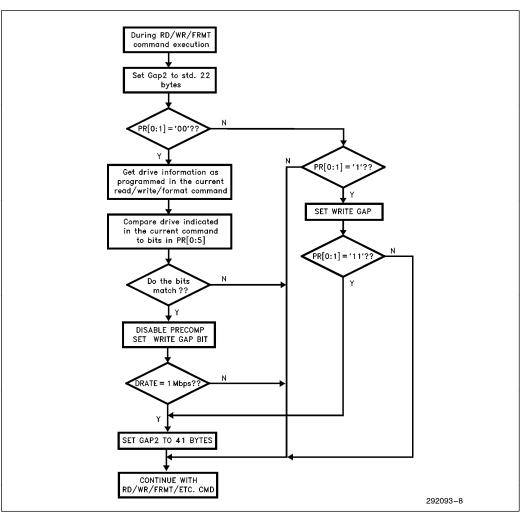

Figures 5a and 5b show a flowchart on how the perpendicular recording mode is implemented on the 82077AA/SL. The perpendicular mode command can be issued during initialization. As shown in Figure 5a the perpendicular command stores the PR value internally. This value is used during the data transfer commands for configuration in order to deal with the perpendicular drives. Table 2 shows how the Gap2 length, VCOEN timing or Write Gate timing is affected. The OW bit is also tested for in this part of the loop. The enhanced perpendicular mode is enabled by setting the OW = 1, setting the Dn bits corresponding to the installed perpendicular drive high and leaving PR[0:1] =  $\frac{100}{100}$

As shown in Figure 5b, the Gap2 length is initially set to the conventional length of 22 bytes. Next the PR[0:1] bits (GAP, WGATE) are checked if they are set to '00'. If the PR[0:1] bits are set to '10' then, perpendicular mode is disabled and conventional mode is retained. If the PR[0:1] = '01' or '11' the VCOEN is

Figure 5a. Perpendicular Command Handling

Figure 5b. During Data Transfer Commands

set to activate 43 bytes or 24 bytes from the start of the Gap2 field, depending on the value as shown in Table 2. After this, PR[0:1] = '11' is checked; if not true (programmed '01') the program is exited with only the VCOEN timing being set for perpendicular mode. If true, however, the Gap2 length is set up for perpendicular mode (note: this is done independent of the data rate). It must be noted that if the PR[0:1] bits are set to '11' then it is up to the user to disable precompensation before accessing perpendicular drives. The other branch of the flowchart refers to setting of PR[0:1] to '00'. In this case, the perpendicular command will have the following effect:

- If any of the Dn bits in PR[2:5] programmed high, then precompensation is automatically disabled (0 ns is selected for the specified drive regardless of the data rate) and VCOEN is set to activate appropriately. All the bits that are set low will enable the 82077 to be configured for conventional mode, i.e., exit the program without modifications (shown Figure 5b).

- 2. Next the data rate is checked for 1 Mbps. If the data rate is at 1 Mbps, then Gap2 length is set to 41 bytes, otherwise, the program is exited without setting up the Gap2 to 41 bytes.

It must be noted that if PR[2:5] are to be recognized in the command the OW bit must be set high. If this bit is low, setting of Dn bits will have no effect. Setting the OW bit will enable the storage of the Dn bit. Also setting PR[0:1] to any other value than '00' will override anything written in the Dn bits. In other words, setting PR[0:1] to a value other than '00' enables the effect of that for all drives. It must be noted that if PR[0:1] bits are set to a value other than '00' then it is recommended not to use the enhanced command mode, i.e., all other bits should be zero. Consider the following examples:

a. PR[0:7] = 0x84; This is the way to use the command in the enhanced mode. In this case, the OW = 1 and D0 is set high. During the data transfer command, if D0 is selected it will be automatically configured for perpendicular mode. If D1 is accessed, however, it will be configured for conventional mode. Similarly, if PR[0:7] = 0x88 then D1 is configured for perpendicular mode and D0 is configured for conventional mode. Software resets do not clear this mode.

## intel

- b. PR[0:7] = 0x03; This is the way to use the command in the old mode. If the user decides to use this mode, then it must be noted that the command has to be issued before every data transfer command. Also when used this way, all the drives are configured for perpendicular mode. The user must also remember to disable precompensation and set the data rate to 1 Mbps while accessing the perpendicular drive in the system. Any software reset clears the command.

- c. PR[0:7] = 0x87; In this case, the OW = 1, D0 = 1and PR[0:1] = 11. This may be called a mixed mode and should be refrained from usage. This is similar to setting PR[0:7] = 0x03, because setting PR[0:1] high overrides automatic configuration. In this case the user has to be aware that precompensation must be disabled and the data rate must be set to 1 Mbps while accessing drive 0. After software reset, bits GAP and WGATE will be cleared, but OW and D0 will retain their previously set values. In other words, after software reset, the part will see PR[0:7] = 0x84. Evidently, this would cause problems and, therefore, it is recommended this mode *not* be used.

- d. PR[0:7] = 0x80; In this case, the OW = 1, Dn = 0 and PR[0:1] = 00. This has the effect of clearing the perpendicular mode command without doing a hardware reset. Another way to do this would be to set PR[0:7] = 0x02; this can then be used to temporarily disable perpendicular mode configuration without affecting the previously programmed Dn values. Software reset following this will reenable the previously programmed enhanced mode command.

Using the enhanced perpendicular command removes the requirement of issuing the perpendicular command for each data transfer command and manually setting the perpendicular configuration.

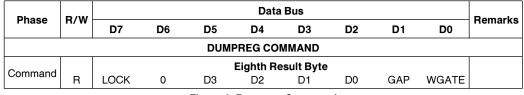

"Software" RESETs (via DOR or DSR registers) will only clear the PR[0:1] values to '0'. Dn bits will retain their previously programmed values. "Hardware" RE-SETs will clear all the programmed bits including OW and Dn bits to '0'. The status of these bits can be determined by issuing the dumpreg command and checking the 8th result byte. This byte will contain the programmed values of the Dn and PR[0:1] bits as shown in Figure 6. The OW bit is *not* returned in this result byte.

Figure 6. Dumpreg Command

#### INTERFACE BETWEEN 82077AA/SL AND THE DRIVE

There is currently no industry-wide standard for the FDC to FDD interface. There are numerous floppy drive vendors, each with their own modes and interface pins to enable 4 MB perpendicular mode. The drive interface not only varies from manufacturer to manufacturer but also within a manufacturer's product line. The differences on the interface mainly originate from configuring the floppy drive into the 4 MB mode. Depending on the drive, the differences can create problems of daisy-chaining a 4 MB drive with the standard 1 MB and 2 MB drives. Of course, for laptops this is not a problem since most of them use a single floppy drive. Lack of an industry standard makes it necessary to look at each drive and build a interface for that particular drive.

The following is a brief discussion about some of the floppy drives available in the market and how these can be interfaced with the 82077AA/SL. It is important to note that although a manufacturer's name may be given in connection with the interface described, Intel does not guarantee that the interface discussed will apply to all the drives from that manufacturer. The main goal is introduce to the reader how to interface the 82077AA/SL with a 4 MB floppy drive.

Previously, for the conventional 1 MB and 2 MB AT mode drives, a single Density Select input was used by floppy drives to select between high density and low density drives. A high on this input enabled high density operation (500 Kbps) whereas a low enabled low density operation (300 Kbps/250 Kbps). This signal

was asserted high or low by the floppy disk controller depending on the data rate programmed. For the 4 MB operation, there are two inputs defined by the floppy drive manufacturers. The polarity of these inputs enables the selected density operation. Implementing this requires at least 1 new pin to be defined on the FDC-FDD interface. Most floppy vendors have elected to take pin 2 (originally density select) and redefine the polarity to conform to one of these new density select inputs and another pin to be the other density select input. However, the new density select on pin 2 is not compatible to the old density select input in many of the floppy drives. This precludes the user from daisy chaining 4 MB drives with conventional drives. Another problem is that the second density select pin varies on its location on the FDC-FDD interface from drive to drive.

The way that the BIOS determines what type of diskette is in what type of drive is by trial and error. The system tries to read the diskette at 250 Kbps; if it fails then it will set the data rate to higher value and retry. The BIOS does this until the right data rate is selected. This method will still be implemented for the 4 MB drives by some BIOS vendors. However, the 4 MB drives available today also have two media sense ID pins that relate to the user what type of media is present in the floppy drive. This information will also require two pins on the FDC-FDD interface. The location of these pins is once again variable from drive to drive.

Some manufacturers have circumvented the entire standardization problem by including an auto configuration in the drive. In these cases, the type of floppy put into the drive is sensed by the hole (each 4/2/1 MB diskette has a hole in different locations identifying it) on the diskette. Then the drive automatically sets itself up for this mode. The BIOS must obviously set up the floppy disk controller for the correct data rate which could be done if the media sense ID was read and decoded as to the data rate. Due to lack of extra pins on the even side of the floppy connector the newer locations of some of the functions are migrating to the odd pins (previously all grounded). Some drive manufacturers have even made this configurable via jumpers. For instance, the new TEAC drives have a huge potpourri of configurations that would satisfy the appetite of some of the most finicky system interfaces.

The 82077AA/SL currently has two output pins DRATE0 and DRATE1 (pins 28 and 29 respectively) which directly reflect the data rate programmed in the DSR and CCR registers. These two pins can be used to select the correct density on the drive. These two can also be used with the combination of DENSEL to select the correct data rate. At the present time the 82077AA/SL does not support media sense ID. However, the user could easily make it readable directly by BIOS. The following is a discussion on what combination of DRATE0, DRATE1, and DENSEL could be used to interface to some of the currently available floppy drives.

#### 1. TEAC 235J-600/Toshiba PD-211/Sony (Old Version)

These were among the first 4 MB drives available in the market. Each of them has a mode select input on pins 2 and 6. The polarity required for each different data rate is as shown below:

| Data<br>Rate        | Capacity | DRATE1 | DRATE0 | MODSEL0<br>pin 2 | MODSEL1<br>pin 6 |

|---------------------|----------|--------|--------|------------------|------------------|

| 1 Mbps              | 4 MB     | 1      | 1      | 1                | 0                |

| 500 Kbps            | 2 MB     | 0      | 0      | 0                | 1                |

| 300 Kbps/<br>1 Mbps | 4 MB     | 0      | 1      | 1                | 1                |

| 250 Kbps            | 1 MB     | 1      | 0      | 0                | 0                |

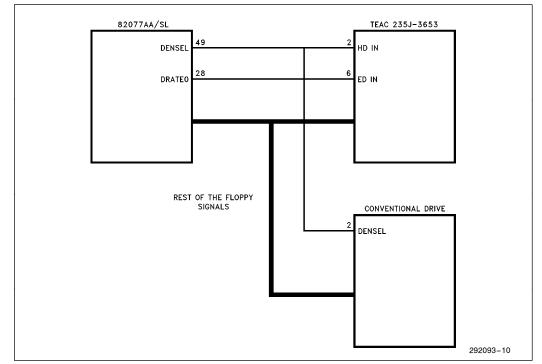

It is clear from the above that DRATE0 = MODSEL0 and MODSEL1 = DRATE1#. This would mean taking the drate signals onto pins 2 and 6 of the FDC-FDD interface. Unfortunately this solution requires an inverting gate. TEAC has recently, however, come out with a new version called TEAC 235J-3653. On this drive there are a number of possible configurations into which the drive can be put into, however, only the best way to interface to the 82077AA/SL will be discussed. The requirements are as shown below. This shows that HDIN = DENSEL (original signal for conventional drives) and EDIN = DRATE0. As suggested in the TEAC spec for method 1, the straps connected are MSC, HI2 (sets HDIN on pin 2), DC34 and EI6 (sets EDIN on pin 6). Pins 4, 29, and 33 are left open. Since pin 2 has the same polarity as the conventional drive requirement and the secondary input is connected via pin 6 (no connect on the conventional drives) daisy chaining this TEAC drive with a conventional drive does not cause any incompatibility. Figure 7 shows how the TEAC can be connected to the 82077AA/SL. It also shows daisy chaining of the TEAC drive with a conventional drive.

| Data<br>Rate        | Capacity | DENSEL | DRATE1 | DRATE0 | HDIN<br>pin 2 | EDIN<br>pin 6 |

|---------------------|----------|--------|--------|--------|---------------|---------------|

| 1 Mbps              | 4 MB     | 1      | 1      | 1      | Х             | 1             |

| 500 Kbps            | 2 MB     | 1      | 0      | 0      | 1             | 0             |

| 300 Kbps/<br>1 Mbps | 4 MB     | 0      | 0      | 1      | Х             | 1             |

| 250 Kbps            | 1 MB     | 0      | 1      | 0      | 0             | 0             |

Figure 7. Interfacing 82077AA/SL to TEAC 235J-3653

#### 2. Panasonic JU-259A (New Version)

This is Panasonic's new drive and has the HDIN signal on pin 2 and EDIN signal on pin 6. The requirements are shown below. This type of interface allows for daisy chaining the Panasonic drive with a conventional drive. The DENSEL signal can be connected to pin 2 and the DRATE0 should be connected to pin 6.

| Data<br>Rate        | Capacity | DENSEL | DRATE1 | DRATE0 | HDIN<br>pin 2 | EDIN<br>pin 6 |

|---------------------|----------|--------|--------|--------|---------------|---------------|

| 1 Mbps              | 4 MB     | 1      | 1      | 1      | 1             | 1             |

| 500 Kbps            | 2 MB     | 1      | 0      | 0      | 1             | 0             |

| 300 Kbps/<br>1 Mbps | 4 MB     | 0      | 0      | 1      | 0             | 1             |

| 250 Kbps            | 1 MB     | 0      | 1      | 0      | 0             | 0             |

#### 3. Mitsubishi MF356C (Model 252UG/788UG)

There are two models of this drive. The 252UG has DENSEL1 on pin 2 and DENSEL0 on pin 33, whereas the 788UG has DENSEL0 located on pin 2 and DENSEL1 located on pin 6. Via jumpers, it is possible to configure the drives to different polarity for the density select line. The following table shows the configuration for the 252UG in which jumper setting is 2MS = I/F and 4MS = I/F.

| Data<br>Rate        | Capacity | DENSEL | DRATE1 | DRATE0 | DENSEL1<br>pin 2 | DENSEL0<br>pin 33 |

|---------------------|----------|--------|--------|--------|------------------|-------------------|

| 1 Mbps              | 4 MB     | 1      | 1      | 1      | 1                | 1                 |

| 500 Kbps            | 2 MB     | 1      | 0      | 0      | 1                | 0                 |

| 300 Kbps/<br>1 Mbps | 4 MB     | 0      | 0      | 1      | 0                | 1                 |

| 250 Kbps            | 1 MB     | 0      | 1      | 0      | 0                | 0                 |

The correct connection requirement is: DENSEL (from 82077AA/SL) = DENSEL1 and DRATE0 = DENSEL0. Although there are other configurations, this provides the best one, since daisy chaining is possible without any problem.

#### 4. Epson SMD-1060

This drive has 3 different modes of operation. Mode B is the best and is similar to Mitsubishi's drives as described above. In this mode, HDI signal is connected to pin 2 and EDI is connected to pin 33. Mode B is enabled by inserting jumpers across 3-4 and 7-8 (SS01 B block) and 1-2 and 3-4 (SS03 block) for the drive with the power separated type (i.e., a connector for the floppy signals and another one for power supply) of 34-pin connector.

| Data<br>Rate        | Capacity | DENSEL | DRATE1 | DRATE0 | HDI<br>pin 2 | EDI<br>pin 33 |

|---------------------|----------|--------|--------|--------|--------------|---------------|

| 1 Mbps              | 4 MB     | 1      | 1      | 1      | 1            | 1             |

| 500 Kbps            | 2 MB     | 1      | 0      | 0      | 1            | 0             |

| 300 Kbps/<br>1 Mbps | 4 MB     | 0      | 0      | 1      | 0            | 1             |

| 250 Kbps            | 1 MB     | 0      | 1      | 0      | 0            | 0             |

As demonstrated by the table, HDI = DENSEL and EDI = DRATE0. These connections would ensure daisy chaining capability without any problems.

### intel

#### 5. Sony MP-F40W-14/15

The dash 14 and 15 are two drives from Sony that handle 4 MB requirements. The MP-F40W-14 has the DENSITY SELECT 1, DENSITY SELECT 0 on pins 2 and 33 respectively, whereas the MP-F40W-15 has the DENSITY SELECT 1, DENSITY SELECT 0 on pins 2 and 6 respectively. As it is obvious from the table below, daisy chaining is easily done if the 82077AA/SL is connected in the PS/2 mode (by tying IDENT low) with either type of drive, the only difference being the location of DENSITY SELECT 0.

| Data<br>Rate        | Capacity | DENSEL<br>PS/2 mode<br>(IDENT = 0) | DRATE1 | DRATE0 | DENSITY<br>SELECT1<br>pin 2 | DENSITY<br>SELECT0<br>pin 6/33 |

|---------------------|----------|------------------------------------|--------|--------|-----------------------------|--------------------------------|

| 1 Mbps              | 4 MB     | 0                                  | 1      | 1      | 0                           | 1                              |

| 500 Kbps            | 2 MB     | 0                                  | 0      | 0      | 0                           | 0                              |

| 300 Kbps/<br>1 Mbps | 4 MB     | 1                                  | 0      | 1      | 1                           | 1                              |

| 250 Kbps            | 1 MB     | 1                                  | 1      | 0      | 1                           | 0                              |

If the drive is used in the PS/2 mode, then DENSITY SELECT1 = DENSEL and DENSITY SELECT0 = DRATE0. To use the drive in AT mode, DENSITY SELECT1 = DRATE1 and DENSITY SELECT0 = DRATE0, as shown below. However, daisy chaining is not possible.

| Data<br>Rate        | Capacity | DENSEL<br>PS/2 mode<br>(IDENT = 0) | DRATE1 | DRATE0 | DENSITY<br>SELECT1<br>pin 2 | DENSITY<br>SELECT0<br>pin 6/33 |

|---------------------|----------|------------------------------------|--------|--------|-----------------------------|--------------------------------|

| 1 Mbps              | 4 MB     | 0                                  | 1      | 1      | 1                           | 1                              |

| 500 Kbps            | 2 MB     | 0                                  | 0      | 0      | 0                           | 0                              |

| 300 Kbps/<br>1 Mbps | 4 MB     | 1                                  | 0      | 1      | 0                           | 1                              |

| 250 Kbps            | 1 MB     | 1                                  | 1      | 0      | 1                           | 0                              |

#### 6. Toshiba ND3571

Toshiba MB drive has the HD mode selection on pin 6 and ED mode selection on pin 2. This causes daisy chaining problems with conventional drives as shown in the figure below:

| Data<br>Rate        | Capacity | DENSEL | DRATE1 | DRATE0 | ED Mode<br>pin 2 | HD Mode<br>pin 6 |

|---------------------|----------|--------|--------|--------|------------------|------------------|

| 1 Mbps              | 4 MB     | 1      | 1      | 1      | 1                | 1                |

| 500 Kbps            | 2 MB     | 1      | 0      | 0      | 0                | 1                |

| 300 Kbps/<br>1 Mbps | 4 MB     | 0      | 0      | 1      | 1                | 0                |

| 250 Kbps            | 1 MB     | 0      | 1      | 0      | 0                | 0                |

The DENSEL from the 82077 is connected to pin 6 and DRATE0 is connected to pin 2.

### intel

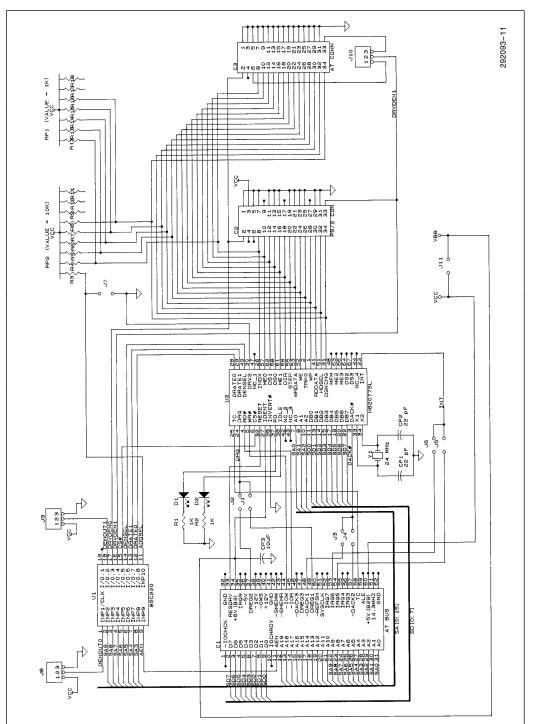

#### 82077SL 4 MB DESIGN

This section presents a design application of a PC/AT compatible floppy disk controller. The 82077SL integrates the entire PC/AT controller design with the exception of the address decode on a single chip. The schematic for this solution is shown in Figure 8. The chip select for the 82077SL is generated by a 85C220  $\mu$ PLD that is programmed to decode addresses 03F0H through 03F7H when AEN is low. The programming equations for the  $\mu$ PLD is in the Intel's .ADF format and can be processed using the IPLSII compiler (available from Intel).

A floppy disk interface is provided by on-chip output buffers with a 40 mA sink capability. The outputs from the disk drive are terminated at the floppy disk controller with a 1 K $\Omega$  resistor pack. The 82077SL disk interface inputs contain a Schmitt trigger input structure for higher noise immunity. The host interface is a similar direct connection with on-chip 12 mA sink capable buffers on DB0–7, INT and DRQ. The schematic shows eleven jumpers numbered J1 through J11. The table below describes the functions of these jumpers as well as their normal connections. The normal connections allow the BIOS to work without modification. In the normal mode, the 82077SL responds to DRQ2 and DACK2# as well as IRQ6. Depending on the type of drive interfaced to this board, the DENOUT0 and DENOUT1 signals can be tied. With the setting to 2-3 on J8 and J9, the default setting is DENSEL on DRVDEN0 and DRATE0 on DRVDEN1. PIN6/33 SELECT is used to set for pin 6 as the EDIN input. The J11 should always be closed. It can be used to measure the current consumption of 82077SL. J7 selects between the primary and secondary address spaces. There are two resistor packs used for pullups on input signals from the floppy drive interface. These resistors are rated at 1K. Please note that if using older 5.25" drives, the pullup on some of them is  $150\Omega$ . Most modem 5.25" drives use a 1K value. In order to ensure the correct value please refer to the floppy drive specification manual.

For further information, please contact your local Intel sales office.

| Jumper | Description                                                            | Normal<br>Connection |

|--------|------------------------------------------------------------------------|----------------------|

| J1     | DRQ1: DMA request 1 used with DACK1 # to allow for DMA transfers       | Open                 |

| J2     | DRQ2: DMA request 2 used with DACK2 # to allow for DMA transfers       | Closed               |

| J3     | DACK1: DMA acknowledge 1 used with DRQ1 to allow for DMA transfers     | Open                 |

| J4     | DACK2: DMA acknowledge 2 used with DRQ2 to allow for DMA transfers     | Closed               |

| J5     | IRQ5: Interrupt line 5 used to generate floppy interrupts              | Open                 |

| J6     | IRQ6: Interrupt line 6 used to generate floppy interrupts              | Closed               |

| J7     | DRV2: Address selection (between 3FX and 37X address ranges)           | Open                 |

| J8     | DENOUT0: Used with DENOUT1 to select the values of DRVDEN1,0           | 2–3                  |

| J9     | DENOUT1: Used with DENOUT0 to select the values of DRVDEN1,0           | 2-3                  |

| J10    | PIN6/33 SELECT: Used to select between pin 6 and pin 33 for EDIN input | 1-2 or 2-3           |

| J11    | V <sub>BB</sub> /V <sub>CC</sub> : Connection between two power layers | Closed               |

Figure 8. 82077SL Evaluation Board

### intel

```

Designer: K. Shah

Company: Intel Corp.

IMD Marketing

Dept:

Date:

April '92

Rev.#:

% The µPLD used in the 82077SL Evaluation board design, Rev.#1.0. %

85C220 dip package

OPTIONS: TURBO = ON

PART:

85C220

INPUTS:

SA9@2, % System Address Inputs %

SA8@3,

SA7@4,

SA6@5,

SA5@6,

SA4@7,

SA3@8,

AEN@9,

<code>DENOUTO@1, \%</code> Maps the DRVDENO and DRVDEN1 to appropriate polarity table \%

DENOUT1@18, \% Maps the DRVDENO and DRVDEN1 to appropriate polarity table \%

ADDSEL@11, \% Selects between primary and secondary address spaces \%

DRATEO@12, \% DRATEO signal from the 82077SL \%

DRATE1@13, % DRATE1 signal from the 82077SL %

DENSEL@14 % DENSEL signal from the 82077SL %

OUTPUTS:

CS_@15, \% 82077SL chip select signal \%

DRVDEN1@16, \% Drive density signal connected to EDIN of the drive \%

DRVDENO@17 % Drive density signal connected to HDIN of the drive %

NETWORK:

% Inputs %

SA9 = INP(SA9)

SA8 = INP(SA8)

SA7 = INP(SA7)

SA6 = INP(SA6)

SA5 = INP(SA5)

SA4 = INP(SA4)

SA3 = INP(SA3)

AEN = INP(AEN)

ADDSEL = INP(ADDSEL)

DRATEO = INP(DRATEO)

DRATE1 = INP(DRATE1)

DENSEL = INP(DENSEL)

DENOUTO = INP(DENOUTO)

DENOUT1 = INP(DENOUT1)

% Outputs %

CS_{-} = CONF(CSeq, V_{CC})

```

```

EQUATIONS:

\% CS_is activated for 3F0-3F7 and 370-377 address spaces \%

CSeq = (AEN' * SA9 * SA8 * SA7' * SA6 * SA5 * SA4 * SA3' * ADDSEL'

+ AEN' * SA9 * SA8 * SA7 * SA6 * SA5 * SA4 * SA3' * ADDSEL)';

% These are the signals generated on DRVDENO and DRVDEN1 for the FDC-FDD

interface

DENOUT1 DENOUTO DRVDENO

DRVDEN1

0

DENSEL

DRATEO

0

0

DENSEL'

DRATEO

1

1

0

DRATE1

DRATEO

1

1

DRATEO

DRATE1

%

DENOeq = DENSEL * (DENOUTO' * DENOUTI') + DENSEL' * (DENOUTO * DENOUTI')

+ DRATEL * (DENOUTO' * DENOUTI) + DRATEO * (DENOUTO * DENOUTI);

DENleq = DRATE1 * (DENOUTO * DENOUT1) + DRATEO * (DENOUTO' + DENOUT1');

END$

```

#### 82077SL Application Note Revision Summary

The following changes have been made since revision 001:

Table 2 kBps was corrected to kbps.

Page 12 3. Mitsubishi MF356C description modified to read: "There are two models of this drive. The 252UG has DENSEL1 on pin 2 and DENSEL0 on pin 33, whereas the 788UG has DENSEL0 located on pin 2 and DENSEL1 located on pin 6. Via jumpers, it is possible to configure the drives to different polarity for the density select lines. The following table shows the configuration for the 252UG in which jumper setting is 2 MS = I/F and 4 MS = I/F."

Figure 8 Arrow added to diagram.

Page 17 Columns corrected to line up properly.